Buildroot

The open-source Buildroot project automates the process of building bootable Linux systems by leveraging the cross-compilation toolchain. Buildroot includes a variety of libraries such as the C standard library and OpenCV, making integration easier. Efinix has a Buildroot configuration for building a bootable Linux environment that you can use with these Efinix boards:

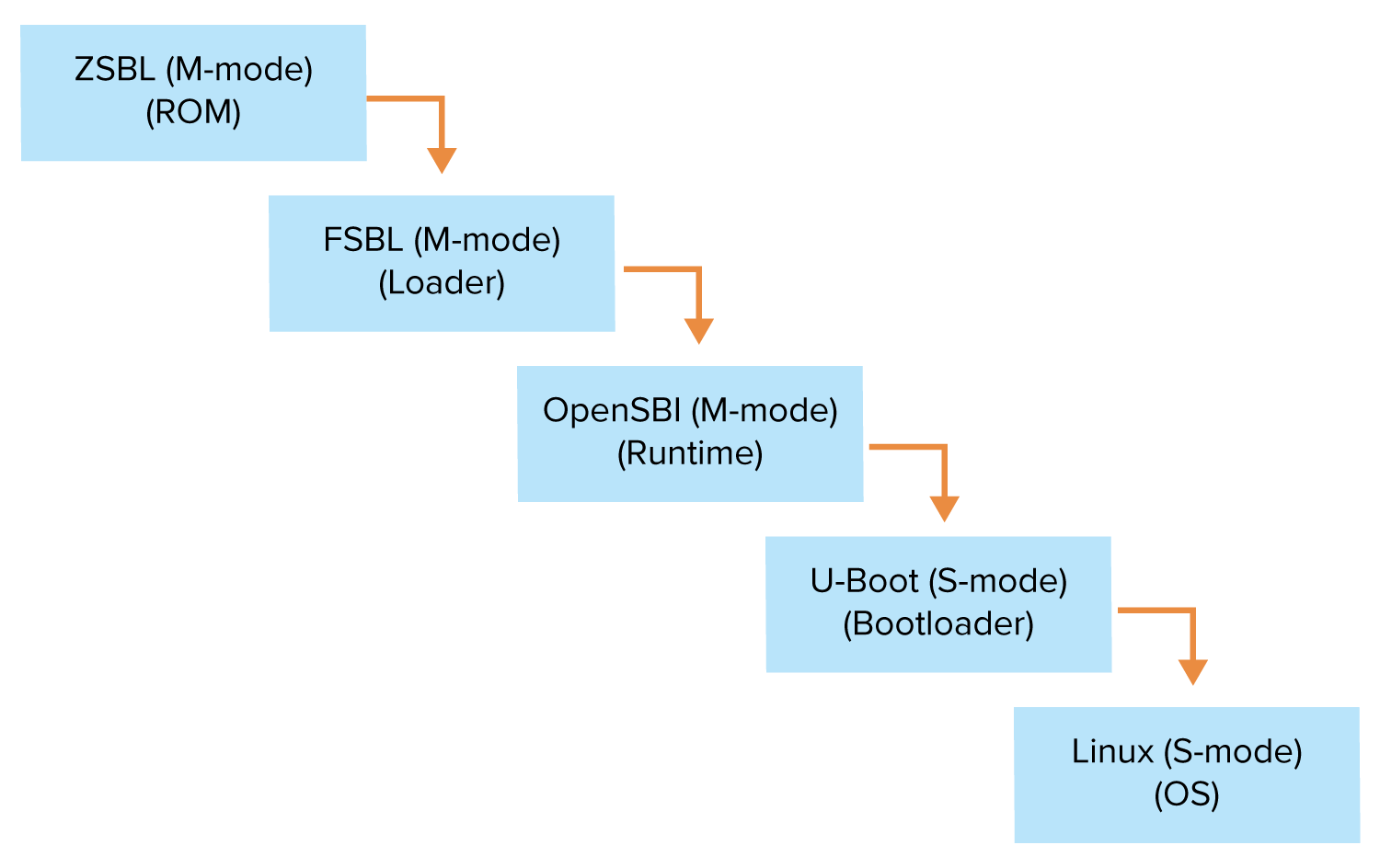

The configuration includes a bootloader (OpenSBI v0.9 and U-boot v2021.04) and the Linux kernel v5.10, which rely on the RISC-V cross-GCC v8.4.0.

To learn more about Buildroot, visit their website.

OpenSBI

The OpenSBI project provides an open-source reference implementation of the RISC-V Supervisor Binary Interface (SBI) specifications for platform-specific firmware executing in M-mode. Learn more at the OpenSBI repository.

U-Boot

U-Boot is a bootloader for embedded boards based on a variety of processors such as RISC-V, PowerPC, ARM, MIPS, and others. U-Boot can be installed in a boot ROM and used to initialize and test the hardware, or to download and run application code. Learn more at the U-Boot repository.

Drivers

Efinix provides Linux drivers for the Sapphire SoC peripherals, such as the APB3, UART, SPI, GPIO, and DMA. Each driver also comes with an example application that illustrates the driver usage.

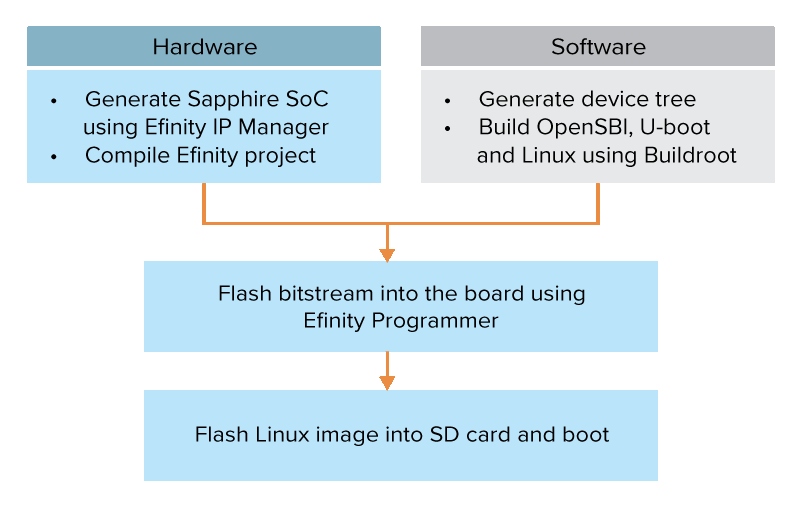

Device Tree Generator

The device tree generator script leverages your Efinity project to describe the SoC-level peripherals that are consumed by the Linux kernel during initialization. Because the Sapphire SoC is configurable, you need to update the device tree when you change the SoC or peripherals. With this script, the developer can easily re-generate the device tree file.