Newsroom > Blog

July 22, 2025

In the rapidly evolving world of microelectronics, there is a relentless push to reduce size and power consumption while increasing compute capability and throughput. Smart edge devices, the internet of things and now Edge AI have only accelerated this trend. While Efinix FPGAs offer unprecedented compute capability, small physical size and the industry’s lowest power consumption, increasingly designers are seeking to reduce this footprint even further for the most demanding of applications. Efinix has stepped up to this challenge and is offering a range of FPGA devices in SiP Packages.

In its simplest form a SiP package is a traditional semiconductor package that contains multiple die. The die may be stacked one on top of the other reducing the overall outline in the package and reducing the package’s physical size. The die may be of different technology process nodes and deliver different functionality. For example a single package may contain a microprocessor, memory, power management and more. The result is greater levels of system integration for more compact end devices. Benefits go beyond physical size however. The smaller physical geometries and trace lengths between the die reduce power consumption associated with driving long traces across a printed circuit board. Additionally short physical lengths increase signal integrity and allow for faster signaling between die. Since much of the work to connect the die and analyze signal integrity has been done by the manufacturer, design complexity and time to market for the end user is reduced.

In many cases, SiP packages provide an alternative to full custom ASIC solutions. Whereas ASICs can cost tens of millions of dollars, and take several years to develop, a SiP solution can be put together in a matter of months for very low NRE. The requirement of course for the SiP solution is that the required functionality already exists in silicon ready for integration. If one of the devices is an FPGA however, the solution is configurable and can be programmed to deliver almost any desired functionality. This makes FPGAs an ideal candidate for SiP packages where they can be programmed for ultimate flexibility. Furthermore, whereas an ASIC has fixed functionality and can rapidly become obsolete, an FPGA SiP can be reconfigured to remain up to date. In the case of evolving standards, for example, an interface die within the SiP that contains a PHY for a particular standard can easily be swapped out for a new standard and the controller logic for the new standard can be implemented in the FPGA fabric.

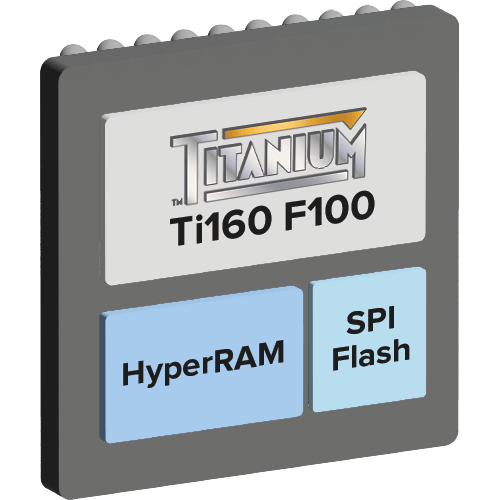

Efinix has SiP package offerings in both its Trion and Titanium families. The Trion T13Q100 and Trion T20Q100 devices both have 16Mb of internal Flash memory as well as the FPGA device. This gives them a self-booting capability and eliminates the need for an external Flash device. The Titanium Ti60F100 has both 16Mb of Flash and 256Mb of HyperRAM in a tiny 5.5mm x 5.5mm package. The Ti60F100 has been enormously successful in applications such as industrial sensors where the tiny package and low power consumption are ideal for harsh industrial environments. The Flash makes the device self-booting and the HyperRAM provides adequate space for frame buffers and video storage.

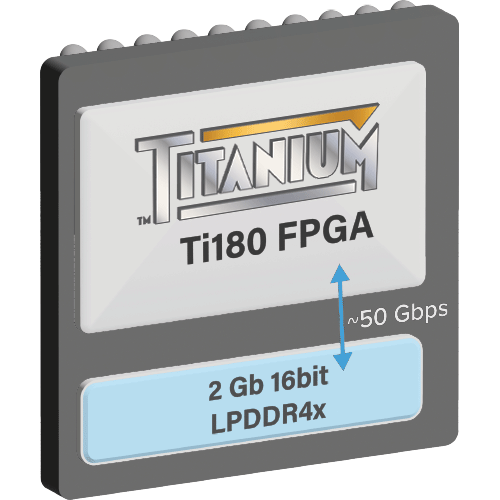

The success of the Ti60F100 inspired Efinix to put together a SiP package for the Titanium Ti180. Here the package contains not only the popular Ti180 FPGA but also 2Gb of embedded LPDDR4 in a 15mm x 15mm package. The embedded LPDDR4 removes the need to have an external memory bus pinned out across traces on the printed circuit board. DDR interfaces are notoriously difficult to design with high signal integrity so this benefit alone reduces design complexity, system power and time to market.

The Ti180 SiP, however, demonstrates a not so obvious benefit. The regular Ti180 has a hardened LPDDR4 interface on the silicon die. This is extremely useful where large quantities of system memory, frame buffers or memory for the RISC-V sub system is needed. The LPDDR interface, however, is very pin intensive on the package and consumes pins that could otherwise be available for user I/O. Efinix delivers the Ti180 in several package options, many of which have the LPDDR4 interface pinned out and available for external memory and some of which prioritize user I/O at the expense of the memory capability. The Ti180 SiP package gets around this dilemma offering both 2Gb of LPDDR4 in package and the full complement of user I/O available on the package pins.

The compelling advantages and versatility of SiP packages means that Efinix will continue to provide SiP options for future families of FPGA. Many such SiP devices are already in design and will be announced in the weeks and months to come. Efinix also makes it’s FPGAs available in die form to strategic partners who use them to put together SiP devices of their own.

SiP devices provide a low cost and low risk alternative to custom silicon. They exhibit high signal integrity and shorten time to market for designers. Where the SiP contains an Efinix FPGA die they deliver ultimate configurability in a low power and high-performance footprint.