Efinix FPGA DSP ブロックを用いた設計

2026年4月17日

現在の最先端のデジタル信号処理 (DSP) ソリューションには、高速性、適応性、そして高精度が求められます。そして、まさにその点において、FPGA (フィールド・プログラマブル・ゲートアレイ) が力を発揮します。強力なハードウェアプラットフォームである FPGA は、卓越した並列処理能力、高いカスタマイズ性、そしてリアルタイムでの柔軟性を提供し、次世代の信号処理アプリケーションを高速化するための理想的なソリューションとなっています。

この分野のリーディングカンパニーである Efinix は、DSP アプリケーションのさまざまな性能レベルに対応するよう設計された、40 nm Trion® シリーズおよび 16 nm Titanium™ シリーズの FPGA を提供しています。これらのデバイスは、高効率な DSP ハードウェア プリミティブを通じて、幅広いリアルタイム信号処理タスクを強力にサポートします。

FPGA における DSP プリミティブとは、デジタル信号処理演算を効率的に実装するために使用される専用のハードウェアブロックです。これらのプリミティブは、一般的に、乗算、加算、累積、シフトなどの機能をサポートしています。

従来の CPU と比較して、FPGA はハードウェアレベルで複数の信号ストリームを並列処理できるため、オーディオ処理、画像処理、通信システム、レーダー、衛星システムなどの高スループット・低遅延アプリケーションにおいて、性能とエネルギー効率の面で大きな利点をもたらします。

本記事では、Efinix FPGA DS Pブロックのアーキテクチャと機能的特徴、および実用的な設計におけるその応用について分析し、これらのハードウェアリソースを活用して効率的な信号処理システムを実装する方法を解説します。

Trion® シリーズ DSP ブロック プリミティブの概要

40 nm プロセスで製造された Trion® シリーズは、最大 400MHz で動作し、18×18 ビットのハードウェア乗算をサポートする DSP モジュールを搭載しており、中程度の複雑さのデジタル信号処理タスクに適しています。動作周波数については、各デバイスのデータシートを参照してください。

EFX_MULT プリミティブ:

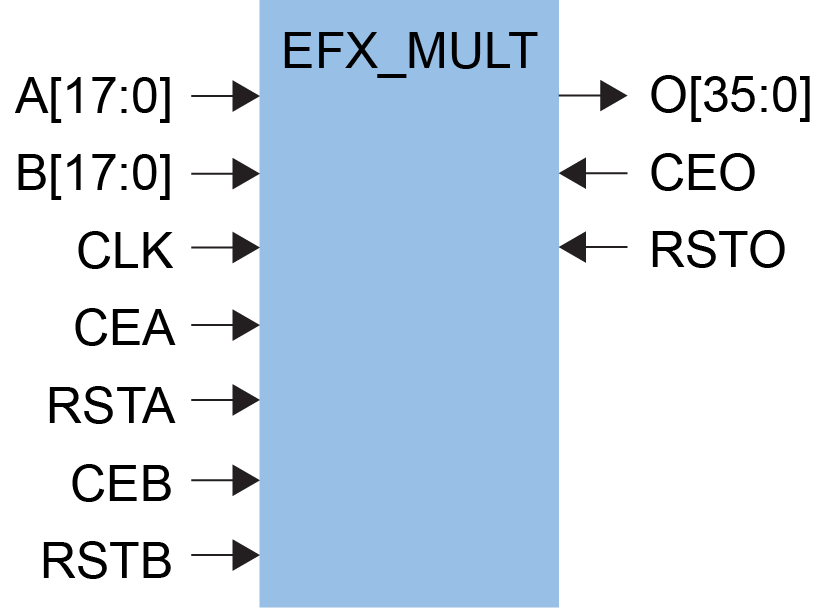

DSP は FPGA 内のモジュールであり、入出力信号と、いくつかの設定可能なパラメータを備えています。次の図は、Trion® DSP プリミティブのブロック図を示しています。

次の表は、EFX_MULT プリミティブの各ポートの詳細を示しています:

| Port Name | Direction | Description |

|---|---|---|

| A[17:0] | Input | Operand A |

| B[17:0] | Input | Operand B |

| CLK | Input | Clock |

| CEA | Input | Clock enable for A |

| RSTA | Input | Set/reset for A |

| CEB | Input | Clock enable for B |

| RSTB | Input | Set/reset for B |

| O[35:0] | Output | Multiplier Output |

| CEO | Input | Clock enable for O |

| RSTO | Input | Set/reset for O |

EFX_MULT プリミティブの詳細については、『Quantam Trion Primitives ユーザーガイド』を参照してください。

概要:

Efinix 40 nm Trion® シリーズ FPGA の DSP モジュールには、18×18 ビットのハードウェア乗算器が搭載されています。この機能を使用するには、機能ブロック図に従って乗算器をインスタンスするだけで済みます。

Titanium™ シリーズ DSP ブロック プリミティブの高度な機能

Efinix Trion® DSP ブロック プリミティブが理解できていれば、Titanium™ DSP モジュールの理解も容易になります。Efinix Titanium シリーズは 16 nm プロセス技術を用いて製造されており、その DSP は 1000 MHz のピーク周波数に達します。動作周波数については、各デバイスのデータシートをご参照ください。

Titanium™ シリーズ FPGA は、Trion® シリーズの DSP よりも高い性能と高度な DSP モジュールを提供します。乗算、加算、減算、累積演算、および 4 ビット可変右シフト演算をサポートしています。複数の動作モードが利用可能であり、デバイスは計算の柔軟性と並列処理能力を向上させます。各 DSP モジュールには、以下の乗算演算をサポートする 4 つの動作モードがあります:

- ノーマルモード — 19×18 整数乗算と 48 ビット加算/減算をサポートします。

- デュアルモード — 11×10 整数乗算と 8×8 整数乗算を各 1 回、および 24 ビット加算/減算を 2 回サポートします。

- クワッドモード — 7×6 整数乗算 1 回と 4×4 整数乗算 3 回、および 4 つの 12 ビット加算/減算演算をサポートします。 (注: 7×6 クワッドモードの出力は 12 ビットに切り捨てられます。)

- 浮動小数点モード — 1 回の融合乗算・加算/減算・積算 (FMA) BFLOAT16 浮動小数点乗算をサポートします。

乗算器/加算器は、SIGNED パラメータの値に応じて、SIGNED モードまたは UNSIGNED モードのいずれかで動作します。 EFX_DSP12 や EFX_DSP24 などの複数の分割された演算子を、同一の EFX_DSP48 インスタンスにマッピングする場合、それらの演算子は同じ SIGNED パラメータ値を共有する必要があります。乗算器の入力は A と B であり、出力結果は加算または減算演算に使用できます。

EFX_DSP48 プリミティブの概要

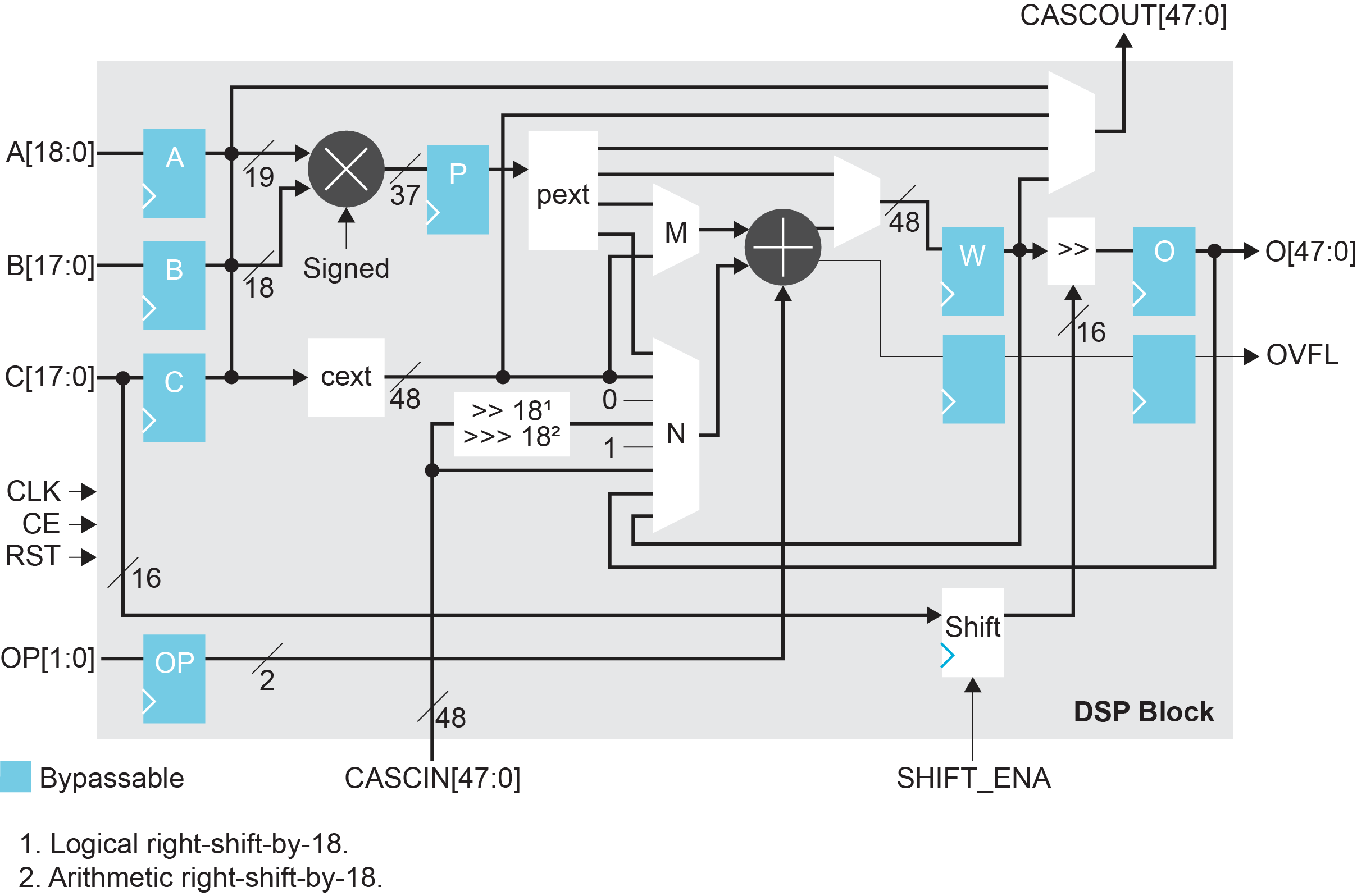

次の図は、Titanium™ DSP ブロックのブロック図を示しています。

青色で表示されているレジスタはバイパス可能です。DSP ブロックには、37 ビットの出力を備えた 19×18 ビットの符号付き/符号なし乗算積算ユニットが含まれています。この出力は、pext へ伝播される前に、P レジスタ (ユーザーが有効化またはバイパス可能) によってオプションでレジスタ化されます。pext は、37 ビットの出力を 48 ビットに拡張するために使用され、以下の 2 つのオプションがあります:

- ALIGN_LEFT: 左揃えで、右側にゼロパディングを行います。

- ALIGN_RIGHT: 右揃えで、符号拡張を行います。この場合、最左端のビットは符号ビット (0 または 1) で埋められます。

pextは複数の出力に接続されています。例えば、M マルチプレクサを経由して加算モジュールに入力したり、CASCOUT_SEL を介して CASCOUT 出力を選択したりすることができます。

出力が加算器モジュールにルーティングされる場合、M_SEL および N_SEL が 2 つの加算器入力を選択し、OP[1:0] が加算演算を決定します (以下の信号説明表に記載の通り)。加算結果は、W_SEL 経由で W レジスタにルーティングされ、最終的に O レジスタから出力されます。

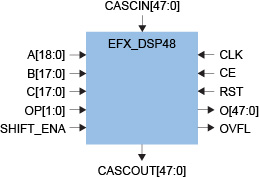

EFX_DSP48 プリミティブは、すべてのモード (NORMAL、DUAL、QUAD、および BFLOAT) において、DSP ブロックの全機能をサポートしています。次の図は、詳細な信号説明表を伴うEFX_DSP48 プリミティブの信号ブロック図です。より深く理解するために、対応する説明および上記の DSP ブロックアーキテクチャ図を参照してください。

| Port Name | Direction | Description |

|---|---|---|

| A[18:0] | Input | Operand A. |

| B[17:0] | Input | Operand B. |

| C[17:0] | Input | Operand C. |

| OP[1:0] | Input | Add/subtract function control. 00: M + N 11: M - N 10: -M + N 11: -M - N |

| SHIFT_ENA | Input | Load the shifter register S from the C input. |

| CASCIN[47:0] | Input | Dedicated input from the DSP block below. |

| CLK | Input | Clock. |

| CE | Input | Clock enable. |

| RST | Input | Reset. |

| O[47:0] | Output | DSP Output. |

| CASCOUT[47:0] | Output | Dedicated output to the DSP block above. |

| OVFL | Output | Overflow/underflow flag. Signed—The operation behaves as you would expect. Unsigned—When OP is 00, the operation behaves as you would expect. For the other operands, it reports overflow or underflow if information is lost during the operation. When using dual or quad mode, the overflow bits are calculated independently and ORed together. |

EFX_DSP48 Operational Modes

通常モード

- 機能 — 19×18 の整数乗算を実行し、37 ビットの結果 (P) を生成します。この結果は 48 ビットに拡張可能です。乗算器は、SIGNED パラメータによって制御される符号付きおよび符号なし演算の両方をサポートしています。

- 拡張とシフト — C 入力は 18 ビットで、C_EXT パラメータを介して 48 ビットまで拡張可能です。論理シフト機能は 0 ~ 15 ビットの右シフトに対応しており、シフトの種類 (算術シフトまたは論理シフト) は DSP ブロックの符号設定によって決まります。SHIFT_ENA ポートが有効になっている場合、シフト値は C 入力から取得されます。

- 適用シナリオ — フィルタ設計や大規模な累積演算など、高精度な乗算を必要とするアプリケーション。

デュアルモード

- 機能 —11×10 の乗算(21 ビットの結果)と 8×8 の乗算 (16 ビットの結果) を同時に実行し、いずれも 24 ビットに拡張されます。

- データパス — C 入力は 2 つの独立したデータパスに割り当てられ、それぞれを個別に拡張可能です。シフト機能はノーマルモードと同様で、動的なシフト制御をサポートします。

- • 適用シナリオ — デュアルチャンネルオーディオ処理や画像処理におけるピクセル演算など、中程度の並列性を伴う信号処理。

クワッドモード

- 機能 — 7×6 の乗算 (13 ビットの結果、12 ビットに切り捨て) と、4×4 の乗算を 3 回 (8 ビットの結果、12 ビットに拡張) を実行します。注: 7×6 の乗算結果は切り捨てられるため、計算範囲が制限されます。

- 特別な処理 — C 入力は 4 つの独立したデータパスに分割されます。シフタは複数のチャネルに対して独立したシフト処理をサポートしており、柔軟性を高めています。

- 適用シナリオ — 機械学習における重み計算やマルチチャネルセンサーデータ処理など、高並列性かつ低精度のタスク。

浮動小数点モード

- 機能 — BFLOAT16 形式の融合乗算加算 (FMA) 演算をサポートし、入力は BFLOAT16 形式、出力は FP32 形式となります。このモードは、AI および機械学習アプリケーション向けに特別に最適化されています。

- 構成要件 — A_REG、B_REG、P_REG、OP_REG、W_REG などのレジスタを有効にする必要があり、P_EXT および C_EXT は ALIGN_RIGHT に設定する必要があります。シフタはバイパスされます。

- 出力形式 — O 出力にはエラーフラグ (オーバーフロー、無効な演算など) が含まれ、ビット [31:0] が FP32 データを表します。

- 適用シナリオ — ニューラルネットワークの推論や科学計算など、浮動小数点演算を多用するアプリケーション。

Efinix Titanium™ シリーズ DSP プリミティブを使用する場合、設計者はリソース効率を最適化し、DSP ブロックの使用率を最小限に抑えるために、オペランドのビット幅要件に基づいて動作モードを選択する必要があります。Titanium DSP ブロックプリミティブの詳細については、『Quantum Titanium Primitives ユーザーガイド』を参照してください。

結論

Efinix FPGA に搭載された DSP ブロックは、Trion® シリーズの 18×18 固定小数点乗算器から、Titanium™ シリーズの高性能 1000MHz マルチモード DSP ブロックに至るまで多岐にわたり、ハードウェアアクセラレーションにおける継続的な最適化と革新を実証しています。

低~中程度の複雑さを伴う組み込み処理から、高スループットのマルチチャンネルリアルタイム信号処理に至るまで、設計者は戦略的な選定と構成を通じてこれらの DSP ブロックを最大限に活用できます。これにより、Efinix FPGA の性能、電力効率、柔軟性を十分に活用し、効率的で信頼性の高いデジタル信号処理システムを開発することが可能になります。

Efinix DSP ブロックのアーキテクチャ、サポート機能、および適用方法に関する体系的な概要を通じて、設計者はその動作原理や実世界の設計への効果的な適用方法を深く理解することができ、より強力で効率的な信号処理ソリューションの開発が可能になります。