USXGMII Multirate Ethernet Core

The USXGMII Multirate Ethernet core, specifically efx_usxgmii_an_37, is a programmable soft IP that implements five flexible data rates: 10G, 5G, 2.5G, 1G, and 100M. Additionally, the USXGMII Multirate Ethernet core supports Ethernet Auto Negotiation Clause 37, that allows changes among the 5 data rates.

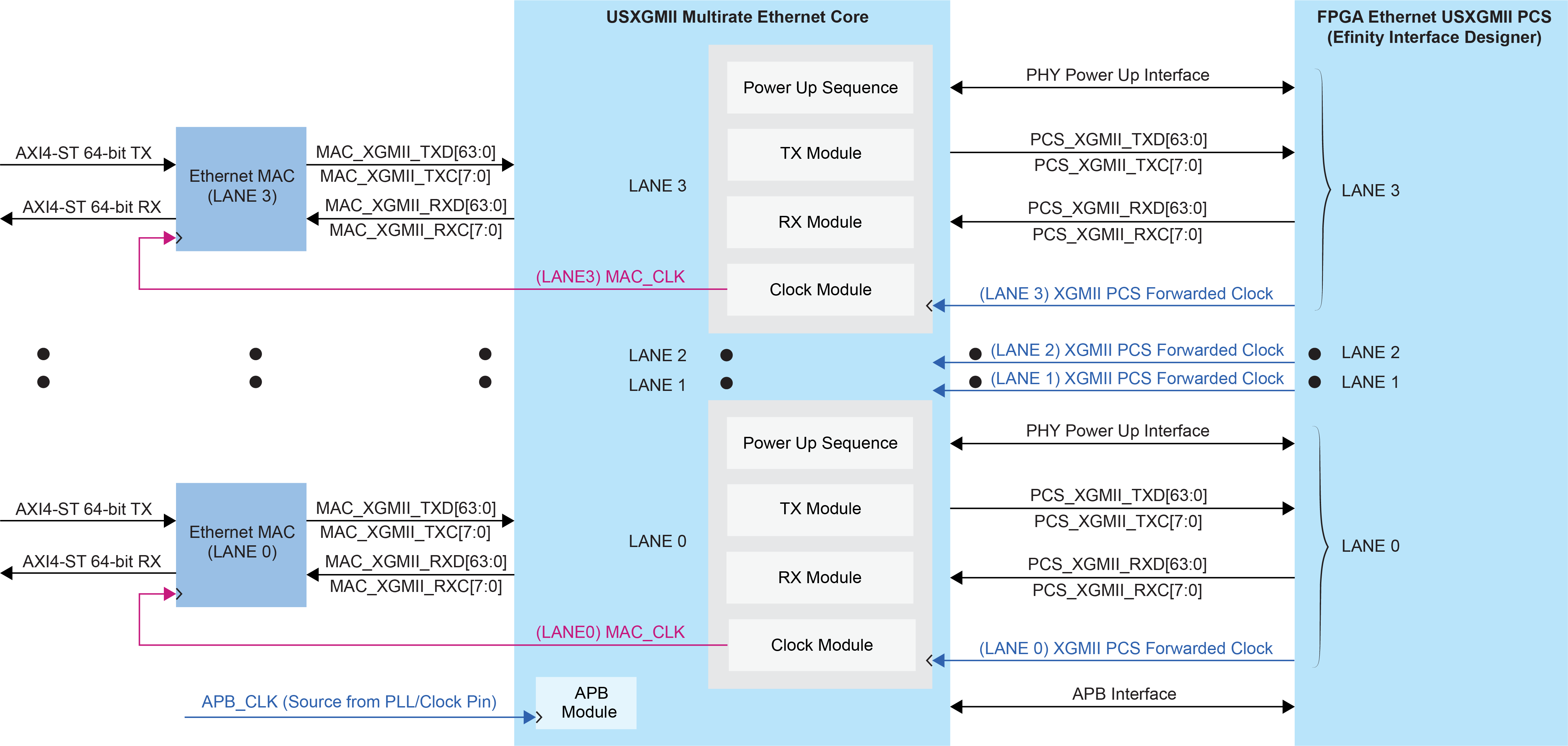

The USXGMII Multirate Ethernet core is designed to interact with both Ethernet MAC and the FPGA Ethernet USXGMII PCS. The data path of the USXGMII Multirate Ethernet core operates in the XGMII format, which consists of 64-bit data and 8-bit control. As shown in USXGMII Multirate Ethernet Interacts with Ethernet MAC and FPGA Ethernet USXGMII PCS Block Diagram, the data path interaction among the Ethernet MAC, USXGMII Multirate Ethernet core, and FPGA Ethernet USXGMII PCS is on a per-lane basis. The configuration of the USXGMII Multirate Ethernet core (to change the data rate and/or enable auto-negotiation) operates along the APB interface and is on a per-quad basis.

USXGMII Multirate Ethernet Interacts with Ethernet MAC and FPGA Ethernet USXGMII PCS Block Diagram

Features

- Compliant with IEEE Std. 802.3-2008 specification

- Supports IEEE Std. 802.3 Clause 37 Auto-negotiation

- Supports flexible data rates of 10G, 5G, 2.5G, 1G, and 100M

- Operates in full-duplex mode only

User Guide