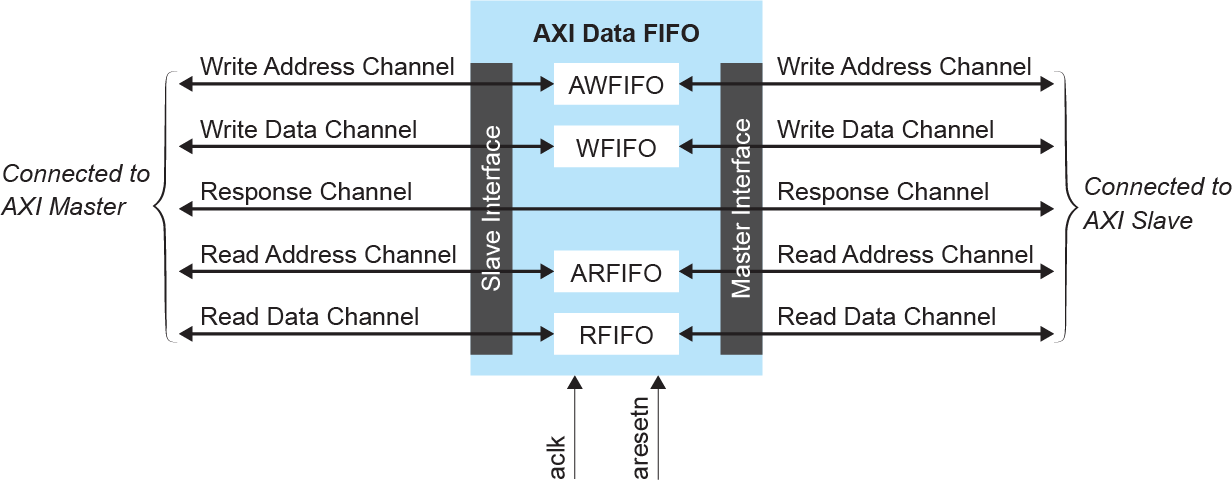

AXI Data FIFO Core

The AXI Data FIFO core provides data buffering for both read and write channels to help prevent stalls, increase throughput, and cross clock domains. It has up to four optional internal FIFOs, one for each channel except the write response channel which is always directly fed through from the MI (Master Interface) to the SI (Slave Interface). You can enable or disable the FIFOs in the read or write address and data channels.

AXI Data FIFO Block Diagram

Features

- Complies with AMBA AXI4-Lite specification (ARM IHI 0022D) and the APB3 specification (ARM IHI 0024B)

- Individually configurable Read and Write datapaths

- 32 and 512 deep FIFO for each channel (excluding write response channel)

- Optional packet FIFO operation to avoid full/empty stalls in the middle of burst

- Verilog HDL RTL and simulation testbench

User Guide