# MIPI D-PHY TX Controller Core User Guide

UG-CORE-MIPI-D-PHY-TX-v1.4 June 2023 www.efinixinc.com

Copyright © 2023. All rights reserved. Efinix, the Efinix logo, the Titanium logo, Quantum, Trion, and Efinity are trademarks of Efinix, Inc. All other trademarks and service marks are the property of their respective owners. All specifications subject to change without notice.

### Contents

| Introduction                             | . 3           |

|------------------------------------------|---------------|

| Features                                 | 3             |

| Device Support                           | 3             |

| Resource Utilization and Performance     | 4             |

| Release Notes                            | 4             |

| Functional Description<br>Ports          | <b>5</b><br>5 |

| IP Manager                               | 11            |

| Customizing the MIPI D-PHY TX Controller | 12            |

| MIPI D-PHY TX Controller Example Design  | 14            |

| MIPI D-PHY TX Controller Testbench       | 15            |

| Revision History                         | 15            |

### Introduction

The MIPI D-PHY is a scalable physical layer for interfacing various components such as cameras and displays to host devices. The MIPI D-PHY TX Controller core allows you to control and configure the MIPI D-PHY TX interface. You use the MIPI D-PHY TX Controller core with the Titanium HSIO pins configured as MIPI TX lanes to build a custom MIPI interface.

Use the IP Manager to select IP, customize it, and generate files. The MIPI D-PHY TX Controller core has an interactive wizard to help you set parameters. The wizard also has options to create a testbench and/or example design targeting an Efinix<sup>®</sup> development board.

### Features

- 1, 2, 4, or 8 configurable data lanes

- Unidirectional (CSI) and bidirectional (DSI) data lane

- High-speed (HS) mode for data communication and low-power (LP) mode for data communication

- 100 MHz core clock frequency

- HS byte clock frequency from 10 MHz to 187 MHz (data rate of 80 Mbps to 1,500 Mbps)

- Continuous HS byte clock and discontinuous HS byte clock

- Supports 8 bits HS data width

- Supports D-PHY-only, D-PHY with CSI, or D-PHY with DSI

- Supports PHY protocol interface (PPI)

- Supports end-of-transmission error, start-of-transmission sync error, control error, and LP escape error

### **Device Support**

| Table 1: | MIPI D-PHY | <b>TX Controller</b> | Core Device | Support |

|----------|------------|----------------------|-------------|---------|

|----------|------------|----------------------|-------------|---------|

| FPGA Family | Supported Device |

|-------------|------------------|

| Trion       | -                |

| Titanium    | All              |

# **Resource Utilization and Performance**

i

Note: The resources and performance values provided are based on some of the supported FPGAs. These values are just guidance and change depending on the device resource utilization, design congestion, and user design.

#### Table 2: Titanium Resource Utilization and Performance

| FPGA    | Data Lane      | Logic and<br>Adders | Flip-flops | Memory<br>Blocks | DSP48<br>Blocks | f <sub>MAX</sub> | (MHz) <sup>(1)</sup> | Efinity <sup>®</sup><br>Version <sup>(2)</sup> |

|---------|----------------|---------------------|------------|------------------|-----------------|------------------|----------------------|------------------------------------------------|

|         |                | / laueno            |            | Dioens           | Brocks          | clk              | clk_byte_HS          | version                                        |

| Ti60    | Unidirectional | 897                 | 302        | 0                | 0               | 330              | 456                  | 2021.2                                         |

| F225 C4 | Bidirectional  | 1,162               | 384        | 0                | 0               | 400              | 434                  | 2021.2                                         |

### **Release Notes**

You can refer to the IP Core Release Notes for more information about the IP core changes. The IP Core Release Notes is available in the Efinity Downloads page under each Efinity software release version.

**Note:** You must be logged in to the Support Portal to view the IP Core Release Notes.

<sup>&</sup>lt;sup>(1)</sup> Using default parameter settings.

<sup>(2)</sup> Using Verilog HDL.

### **Functional Description**

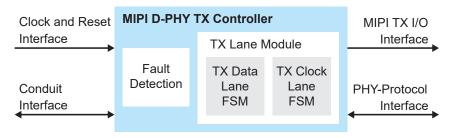

The MIPI D-PHY TX Controller consists of a fault detection block, HS data de-skew calibration block, data lane FSM block, and clock lane FSM block.

Figure 1: MIPI D-PHY TX Controller System Block Diagram

#### Ports

| Table | 3: | Clock | and | Reset | Interface |

|-------|----|-------|-----|-------|-----------|

|-------|----|-------|-----|-------|-----------|

| Port            | Direction | Description                                                   |

|-----------------|-----------|---------------------------------------------------------------|

| clk             | Input     | IP core clock consumed by controller logics. 100 MHz.         |

| reset_n         | Input     | IP core reset signal.                                         |

| clk_byte_HS     | Input     | MIPI TX parallel clock. This is a HS mode transmission clock. |

| reset_byte_HS_n | Input     | MIPI TX parallel clock reset signal.                          |

#### Table 4: MIPI TX I/O Interface

| Port                                  | Direction | Description                                                        |

|---------------------------------------|-----------|--------------------------------------------------------------------|

| Tx_LP_CLK_N                           | Output    | LP mode TX clock single-ended N signal.                            |

| Tx_LP_CLK_P                           | Output    | LP mode TX clock single-ended P signal.                            |

| Tx_LP_CLK_N_OE                        | Output    | Output enable for LP mode TX clock single-ended N signal.          |

| Tx_LP_CLK_P_OE                        | Output    | Output enable for LP mode TX clock single-ended P signal.          |

| Tx_HS_enable_C                        | Output    | Signal to enable HS mode clock lane.                               |

| Tx_HS_C [7:0]                         | Output    | HS mode differential clock bus.                                    |

| Tx_LP_D_P<br>[NUM_DATA_LANE-1:0]      | Output    | LP mode TX data single-ended P signal.                             |

| Tx_LP_D_N<br>[NUM_DATA_LANE-1:0]      | Output    | LP mode TX data single-ended N signal.                             |

| Tx_LP_D_P_OE<br>[NUM_DATA_LANE-1:0]   | Output    | Output enable for LP mode TX data single-ended P signal.           |

| Tx_LP_D_N_OE<br>[NUM_DATA_LANE-1:0]   | Output    | Output enable for LP mode TX data single-ended N signal.           |

| Tx_HS_D_0[7:0]                        | Output    | HS mode differential lane 0 data bus.                              |

| Tx_HS_D_1[7:0]                        | Output    | HS mode differential lane 1 data bus.                              |

| Tx_HS_D_2[7:0]                        | Output    | HS mode differential lane 2 data bus.                              |

| Tx_HS_D_3[7:0]                        | Output    | HS mode differential lane 3 data bus.                              |

| Tx_HS_D_4[7:0]                        | Output    | HS mode differential lane 4 data bus.                              |

| Tx_HS_D_5[7:0]                        | Output    | HS mode differential lane 5 data bus.                              |

| Tx_HS_D_6[7:0]                        | Output    | HS mode differential lane 6 data bus.                              |

| Tx_HS_D_7[7:0]                        | Output    | HS mode differential lane 7 data bus.                              |

| Tx_HS_enable_D<br>[NUM_DATA_LANE-1:0] | Output    | Signal to enable HS mode data lane.                                |

| Rx_LP_D_P                             | Input     | LP mode RX data single-ended P signal for bidirectional data lane. |

| Rx_LP_D_N                             | Input     | LP mode RX data single-ended N signal for bidirectional data lane. |

| Table 5 | 5: PHY-P | rotocol | Interface |

|---------|----------|---------|-----------|

|---------|----------|---------|-----------|

| Port                                              | Direction | Description                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TxRequestHS<br>[NUM_DATA_LANE-1:0]                | Input     | HS Transmit Request and Data Valid.<br>A low-to-high transition causes the lane module to initiate a start-of-<br>transmission sequence. A high-to-low transition on causes the lane<br>module to initiate an end-of-transmission sequence.<br>This active-high signal also indicates that the protocol is driving valid data<br>on TxDataHS to be transmitted.                        |

| TxDataHS_0 [7:0]                                  | Input     | HS Transmit Data Bus.<br>HS data to be transmitted.                                                                                                                                                                                                                                                                                                                                    |

| TxDataHS_1 [7:0]                                  | Input     | HS Transmit Data Bus.<br>HS data to be transmitted.                                                                                                                                                                                                                                                                                                                                    |

| TxDataHS_2 [7:0]                                  | Input     | HS Transmit Data Bus.<br>HS data to be transmitted.                                                                                                                                                                                                                                                                                                                                    |

| TxDataHS_3 [7:0]                                  | Input     | HS Transmit Data Bus.<br>HS data to be transmitted.                                                                                                                                                                                                                                                                                                                                    |

| TxDataHS_4 [7:0]                                  | Input     | HS Transmit Data Bus.<br>HS data to be transmitted.                                                                                                                                                                                                                                                                                                                                    |

| TxDataHS_5 [7:0]                                  | Input     | HS Transmit Data Bus.<br>HS data to be transmitted.                                                                                                                                                                                                                                                                                                                                    |

| TxDataHS_6 [7:0]                                  | Input     | HS Transmit Data Bus.<br>HS data to be transmitted.                                                                                                                                                                                                                                                                                                                                    |

| TxDataHS_7 [7:0]                                  | Input     | HS Transmit Data Bus.<br>HS data to be transmitted.                                                                                                                                                                                                                                                                                                                                    |

| TxSkewCalHS <sup>(3)</sup><br>[NUM_DATA_LANE-1:0] | Input     | HS Transmit Skew Calibration.<br>This is an optional signal to initiate the periodic deskew burst at the<br>transmitter.<br>A low-to-high transition causes the PHY to initiate the transmission of a<br>skew calibration pattern. A high-to-low transition causes the PHY to end<br>the transmission of a skew calibration pattern, and initiate an end-of-<br>transmission sequence. |

| TxReadyHS<br>[NUM_DATA_LANE-1:0]                  | Output    | HS Transmit Ready.<br>This active-high signal indicates that TxDataHS is accepted by the lane<br>module to be serially transmitted.                                                                                                                                                                                                                                                    |

| TxRequestEsc<br>[NUM_DATA_LANE-1:0]               | Input     | Escape Mode Transmit Request.<br>This active-high signal is used to request escape sequences.                                                                                                                                                                                                                                                                                          |

| TxStopStateD<br>[NUM_DATA_LANE-1:0]               | Output    | Lane in Stop State.<br>This active-high signal indicates that the lane module is in stop state.                                                                                                                                                                                                                                                                                        |

| TxUlpsExit<br>[NUM_DATA_LANE-1:0]                 | Input     | Transmit ULPS Exit Sequence.<br>This active-high signal is asserted when ULPS is active and the protocol is<br>ready to leave ULPS.                                                                                                                                                                                                                                                    |

| TxUlpsActiveNot<br>[NUM_DATA_LANE-1:0]            | Output    | ULPS (not) Active.<br>This active-low signal is asserted to indicate that the lane is in ULPS.                                                                                                                                                                                                                                                                                         |

<sup>&</sup>lt;sup>(3)</sup> HS Transmit Skew Calibration is not supported in v2021.1EA.

| Port                              | Direction | Description                                                                                                                                                                                                                      |

|-----------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TxUlpsEsc<br>[NUM_DATA_LANE-1:0]  | Input     | Escape Mode Transmit ULPS.<br>This active-high signal is asserted with TxRequestEsc to cause the lane<br>module to enter the ULPS.                                                                                               |

| TxLpdtEsc<br>[NUM_DATA_LANE-1:0]  | Input     | Escape Mode Transmit LP Data.<br>This active-high signal is asserted with TxRequestEsc to cause the lane<br>module to enter LP data transmission mode.                                                                           |

| TxValidEsc<br>[NUM_DATA_LANE-1:0] | Input     | Escape Mode Transmit Data Valid.<br>This active-high signal indicates that the protocol is driving valid data on<br>TxDataEsc to be transmitted.                                                                                 |

| TxDataEsc_0 [7:0]                 | Input     | Escape Mode Transmit Data.<br>This is the eight bit Escape Mode data to be transmitted in LP data<br>transmission mode. The signal connected to TxDataEsc_0[0] is transmitted<br>first. Data is captured on rising edges of clk. |

| TxDataEsc_1 [7:0]                 | Input     | Escape Mode Transmit Data.<br>This is the eight bit Escape Mode data to be transmitted in LP data<br>transmission mode. The signal connected to TxDataEsc_1[0] is transmitted<br>first. Data is captured on rising edges of clk. |

| TxDataEsc_2 [7:0]                 | Input     | Escape Mode Transmit Data.<br>This is the eight bit Escape Mode data to be transmitted in LP data<br>transmission mode. The signal connected to TxDataEsc_2[0] is transmitted<br>first. Data is captured on rising edges of clk. |

| TxDataEsc_3 [7:0]                 | Input     | Escape Mode Transmit Data.<br>This is the eight bit Escape Mode data to be transmitted in LP data<br>transmission mode. The signal connected to TxDataEsc_3[0] is transmitted<br>first. Data is captured on rising edges of clk. |

| TxDataEsc_4 [7:0]                 | Input     | Escape Mode Transmit Data.<br>This is the eight bit Escape Mode data to be transmitted in LP data<br>transmission mode. The signal connected to TxDataEsc_4[0] is transmitted<br>first. Data is captured on rising edges of clk. |

| TxDataEsc_5 [7:0]                 | Input     | Escape Mode Transmit Data.<br>This is the eight bit Escape Mode data to be transmitted in LP data<br>transmission mode. The signal connected to TxDataEsc_5[0] is transmitted<br>first. Data is captured on rising edges of clk. |

| TxDataEsc_6 [7:0]                 | Input     | Escape Mode Transmit Data.<br>This is the eight bit Escape Mode data to be transmitted in LP data<br>transmission mode. The signal connected to TxDataEsc_6[0] is transmitted<br>first. Data is captured on rising edges of clk. |

| TxDataEsc_7 [7:0]                 | Input     | Escape Mode Transmit Data.<br>This is the eight bit Escape Mode data to be transmitted in LP data<br>transmission mode. The signal connected to TxDataEsc_7[0] is transmitted<br>first. Data is captured on rising edges of clk. |

| TxReadyEsc<br>[NUM_DATA_LANE-1:0] | Output    | Escape Mode Transmit Ready.<br>This active-high signal indicates that TxDataEsc is accepted bythe lane<br>module to be serially transmitted. TxReadyEsc is valid on rising edges of<br>TxClkEsc.                                 |

| Port               | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TxRequestHSc       | Input     | HS Transmit Request and Data Valid.<br>A low-to-high transition causes the lane module to initiate a start-of-<br>transmission sequence. A high-to-low transition causes the lane module to<br>initiate an end-of-transmission sequence.<br>This active-high signal causes the lane module to begin transmitting a HS<br>clock.                                                                                                                                                                                                                                           |

| TxReadyHSc         | Output    | HS Transmit Ready.<br>This active-high signal indicates that the lane is transmitting a HS clock.                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| TxUlpsClk          | Input     | Transmit ULPS on Clock Lane.<br>This active-high signal is asserted to cause a Clock lane module to enter<br>the ULPS.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| TxUlpsExitClk      | Input     | Transmit ULPS Exit Sequence.<br>This active-high signal is asserted when ULPS is active and the protocol is<br>ready to leave ULPS.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| TxUlpsActiveClkNot | Output    | ULPS (not) Active.<br>This active-low signal is asserted to indicate that the lane is in ULPS.                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| TxStopStateC       | Output    | Lane in Stop state.<br>This active-high signal indicates that the lane module is in stop state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TurnRequest        | Input     | Turnaround Request.<br>This active high signal is used to indicate that the protocol desires to<br>initiate a bidirectional data lane turnaround, to allow the other side<br>to begin transmissions. TurnRequest is valid on rising edge of clk.<br>TurnRequest is only meaningful for a bidirectional data lane module that<br>is currently the transmitter (Direction=0). If the bidirectional data lane<br>module is in receive mode (Direction=1), this signal is ignored. A low-<br>to-high transition on TurnRequest can only happen when Stopstate is<br>asserted. |

| TurnRequest_done   | Output    | Indicates that the RX D-PHY acknowledges the bus turnaround or timeout.<br>If this signal is high together with turnaround timeout, it indicates that<br>there is no acknowledgement from the RX on the turnaround request.                                                                                                                                                                                                                                                                                                                                               |

| Turnaround_timeout | Output    | Indicates that there is no acknowledgement from the RX D-PHY for the turnaround request and TX D-PHY ends the turnaround request.                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| RxUlpsEsc          | Output    | Escape ULPS.<br>This active-high signal is asserted to indicate that the lane module has<br>entered the ULPS, due to the detection of a received ULPS command. This<br>signal is used only in Bidir data lane mode.                                                                                                                                                                                                                                                                                                                                                       |

| RxUlpsActiveNot    | Output    | ULPS (not) Active.<br>This active-low signal is asserted to indicate that the lane is in ULPS. This<br>signal is used only in bidirectional data lane mode.                                                                                                                                                                                                                                                                                                                                                                                                               |

| RxLPDTEsc          | Output    | Escape LP Data Receive Mode.<br>This active-high signal is asserted to indicate that the lane module is in<br>LP data receive mode. This signal is used only in bidirectional data lane<br>mode.                                                                                                                                                                                                                                                                                                                                                                          |

| RxValidEsc         | Output    | Escape LP Data Receive Mode.<br>This active-high signal is asserted to indicate that the lane module is in<br>LP data receive mode. This signal is used only in bidirectional data lane<br>mode.                                                                                                                                                                                                                                                                                                                                                                          |

| Port               | Direction | Description                                                                                                                                                                                                                                             |

|--------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RxStopState        | Output    | Lane in Stop State.                                                                                                                                                                                                                                     |

|                    |           | This active-high signal indicates that the lane module is currently in stop state. This signal is used only in bidirectional data lane mode.                                                                                                            |

| RxDataEsc [7:0]    | Output    | Escape Mode Receive Data.                                                                                                                                                                                                                               |

|                    |           | This is the eight-bit escape mode LP data received by the lane module.<br>The signal connected to RxDataEsc[0] was received first. Data is<br>transferred on rising edges of clk. This signal is used only in bidirectional<br>data lane mode.          |

| RxTriggerEsc [3:0] | Output    | Escape Mode Receive Trigger.                                                                                                                                                                                                                            |

|                    |           | These active high signals indicate that a trigger event has been received.<br>The asserted RxTriggerEsc signal remains active until a stop state is<br>detected on the lane interconnect.                                                               |

|                    |           | Applicable to bidirectional mode only.                                                                                                                                                                                                                  |

|                    |           | RxTriggerEsc[0] corresponds to reset-trigger.                                                                                                                                                                                                           |

|                    |           | RxTriggerEsc[1] corresponds to entry sequence for HS test mode trigger.                                                                                                                                                                                 |

|                    |           | RxTriggerEsc[2] corresponds to unknown-4 trigger.                                                                                                                                                                                                       |

|                    |           | RxTriggerEsc[3] corresponds to unknown-5 trigger.                                                                                                                                                                                                       |

| ErrEsc             | Output    | Escape Entry Error.                                                                                                                                                                                                                                     |

|                    |           | If an unrecognized escape entry command is received in LP mode,<br>this active-high signal is asserted and remains asserted until the next<br>transaction starts, so that the protocol can properly process the error.                                  |

|                    |           | Applicable to bidirectional mode only.                                                                                                                                                                                                                  |

| ErrControl         | Output    | Control Error.                                                                                                                                                                                                                                          |

|                    |           | This active-high signal is asserted when an incorrect line state sequence<br>is detected in LP and ALP modes. Once asserted, this signal remains<br>asserted until the next transaction starts, so that the protocol can properly<br>process the error. |

|                    |           | Applicable to bidirectional mode only.                                                                                                                                                                                                                  |

#### **IP** Manager

The Efinity<sup>®</sup> IP Manager is an interactive wizard that helps you customize and generate Efinix<sup>®</sup> IP cores. The IP Manager performs validation checks on the parameters you set to ensure that your selections are valid. When you generate the IP core, you can optionally generate an example design targeting an Efinix development board and/or a testbench. This wizard is helpful in situations in which you use several IP cores, multiple instances of an IP core with different parameters, or the same IP core for different projects.

Note: Not all Efinix IP cores include an example design or a testbench.

#### Generating a Core with the IP Manager

The following steps explain how to customize an IP core with the IP Configuration wizard.

- 1. Open the IP Catalog.

- 2. Choose an IP core and click Next. The IP Configuration wizard opens.

- 3. Enter the module name in the Module Name box.

- 4. Customize the IP core using the options shown in the wizard. For detailed information on the options, refer to the IP core's user guide or on-line help.

- 5. (Optional) In the **Deliverables** tab, specify whether to generate an IP core example design targeting an Efinix<sup>®</sup> development board and/or testbench. For SoCs, you can also optionally generate embedded software example code. These options are turned on by default.

- 6. (Optional) In the Summary tab, review your selections.

- 7. Click Generate to generate the IP core and other selected deliverables.

- 8. In the Review configuration generation dialog box, click Generate. The Console in the Summary tab shows the generation status.

**Note:** You can disable the **Review configuration generation** dialog box by turning off the **Show Confirmation Box** option in the wizard.

9. When generation finishes, the wizard displays the Generation Success dialog box. Click OK to close the wizard.

The wizard adds the IP to your project and displays it under IP in the Project pane.

#### **Generated Files**

The IP Manager generates these files and directories:

- **<module name>\_define.vh**—Contains the customized parameters.

- **<module name>\_tmpl.v**—Verilog HDL instantiation template.

- **cmodule name>\_tmpl.vhd**—VHDL instantiation template.

- <module name>.v—IP source code.

- **settings.json**—Configuration file.

- <kit name>\_devkit—Has generated RTL, example design, and Efinity<sup>®</sup> project targeting a specific development board.

**Note:** Refer to the IP Manager chapter of the Efinity<sup>®</sup> Software User Guide for more information about the Efinity<sup>®</sup> IP Manager.

# Customizing the MIPI D-PHY TX Controller

You can choose to generate the testbench when generating the core in the IP Manager Configuration window.

**Note:** You must include all **.v** files generated in the **/testbench** directory in your simulation.

Efinix provides a simulation script for you to run the testbench quickly using the Modelsim software. To run the Modelsim testbench script, run vsim -do modelsim.do in a terminal application. You must have Modelsim installed on your computer to use this script.

Table 6: MIPI D-PHY TX Controller Core Parameter

i

| Name              | Option                                            | Description                                                                                                                                   |  |  |  |  |

|-------------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| tLPX (ns)         | Values according to MIPI<br>D-PHY specifications. | Soft D-PHY timing parameter in ns.<br>Default: 50                                                                                             |  |  |  |  |

| HS BYTECLK (MHz)  | 10 - 187                                          | MIPI parallel clock frequency in MHz to support<br>data rate of 80 Mbps to 1,500 Mbps.<br>Default: 100                                        |  |  |  |  |

| Data Lane         | 1, 2, 4, 8                                        | Number of data lanes.<br>Default: 4                                                                                                           |  |  |  |  |

| DPHY Clock Mode   | Continuous, Discontinuous                         | Enables discontinuous or continuous HS clock.<br>Default: continuous                                                                          |  |  |  |  |

| tLP_EXIT (ns)     | Values according to MIPI<br>D-PHY specifications. | Soft D-PHY timing parameter in ns.<br>Default: 100                                                                                            |  |  |  |  |

| tWAKEUP (ns)      | Values according to MIPI<br>D-PHY specifications. | Soft D-PHY timing parameter in ns.<br>Default: 1000                                                                                           |  |  |  |  |

| tHS_EXIT (ns)     | Values according to MIPI<br>D-PHY specifications. | Soft D-PHY timing parameter in ns.<br>Default: 100                                                                                            |  |  |  |  |

| tHS_ZERO (ns)     | Values according to MIPI<br>D-PHY specifications. | Soft D-PHY timing parameter in ns.<br>Default: 105                                                                                            |  |  |  |  |

| tHS_TRAIL (ns)    | Values according to MIPI<br>D-PHY specifications. | Soft D-PHY timing parameter in ns before adding<br>4UI.<br>Actual THS TRAIL = tHS_TRAIL_NS + 4UI or 8UI<br>(whichever bigger).<br>Default: 60 |  |  |  |  |

| tCLK_ZERO (ns)    | Values according to MIPI<br>D-PHY specifications. | Soft D-PHY timing parameter in ns.<br>Default: 262                                                                                            |  |  |  |  |

| tCLK_TRAIL (ns)   | Values according to MIPI<br>D-PHY specifications. | Soft D-PHY timing parameter in ns.<br>Default: 60                                                                                             |  |  |  |  |

| tCLK_POST (ns)    | Values according to MIPI<br>D-PHY specifications. | Soft D-PHY timing parameter in ns before adding<br>UI52.<br>Default: 60                                                                       |  |  |  |  |

| tCLK_PREPARE (ns) | Values according to MIPI<br>D-PHY specifications. | Soft D-PHY timing parameter in ns.<br>Default: 38                                                                                             |  |  |  |  |

| Name                        | Option                                            | Description                                                                                                                                                                                             |

|-----------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| tCLK_PRE (ns)               | Values according to MIPI<br>D-PHY specifications. | Soft D-PHY timing parameter in ns before adding<br>UI52.<br>Default: 10                                                                                                                                 |

| Bus Turnaround Timeout (ns) | _                                                 | Bus turnaround timeout parameter in ns. If the D-<br>PHY RX does not respond within this period, D-<br>PHY TX ends the turnaround request.<br>Applicable to bidirectional mode only.<br>Default: 100000 |

| tD_TERM_EN (ns)             | Values according to MIPI<br>D-PHY specifications. | Soft D-PHY timing parameter in ns.<br>Applicable to bidirectional mode only.<br>Default: 35                                                                                                             |

| tHS_PREPARE_ZERO (ns)       | Values according to MIPI<br>D-PHY specifications. | Soft D-PHY timing parameter in ns.<br>Applicable to bidirectional mode only.<br>Default: 145                                                                                                            |

| Enable Bidir Mode           | 0 or 1                                            | Enable bidirectional data lane.<br>Applicable to bidirectional mode only.<br>Default: 1                                                                                                                 |

| CLOCK_FREQ_MHZ              | 40 - 100                                          | Core clock frequency in MHz.<br>Default: 100                                                                                                                                                            |

| tHS_PREPARE (ns)            | Values according to MIPI<br>D-PHY specifications. | Soft D-PHY timing parameter in ns.<br>Default: 50                                                                                                                                                       |

### MIPI D-PHY TX Controller Example Design

You can choose to generate the example design when generating the core in the IP Manager Configuration window. Compile the example design project and download the **.hex** or **.bit** file to your board.

Important: Efinix tested the example design generated with the default parameter options only.

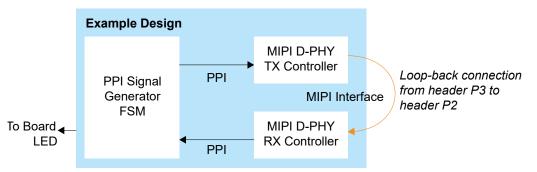

The example design targets the Titanium Ti60 F225 Development Board. The design instantiates both MIPI D-PHY TX Controller and MIPI D-PHY RX Controller cores. This design requires a female-to-female QTE header cable.

The PPI signal generator FSM generates a data and sends back the data through the MIPI D-PHY TX Controller and MIPI D-PHY RX Controller. The PPI signal generator FSM compares the sent and received data, and outputs the results using the board LEDs.

Figure 2: MIPI D-PHY TX Controller Core Example Design

After power-up, LEDs D19 and D18 turn on if the received data and the generated data matches. The RX clock to RX data skew can vary from board to board, therefore, there is a possibility that the RX clock might not be able to capture the RX data correctly. In this case, the LEDs do not turn on. Use the **Static Mode Delay Setting** in the Interface Designer for the mipi\_dphy\_rx\_clk to adjust the delay up or down.

Table 7: Example Design Implementation

| FPGA         | Data Lane      | Logic Flip-<br>and flops | Flip-<br>flops | Memory<br>Blocks | DSP48<br>Blocks | f <sub>MAX</sub> (MHz) <sup>(4)</sup> |      |      | Efinity <sup>®</sup><br>Version <sup>(5)</sup> |

|--------------|----------------|--------------------------|----------------|------------------|-----------------|---------------------------------------|------|------|------------------------------------------------|

|              |                | Adders                   | nopo           | Dioens           | Brocks          | clk1                                  | clk2 | clk3 | version.                                       |

| Ti60 F225 C4 | Unidirectional | 1,632                    | 783            | 0                | 0               | 295                                   | 331  | 340  | 2021.2                                         |

|              | Bidirectional  | 1,931                    | 913            | 0                | 0               | 317                                   | 353  | 331  | 2021.2                                         |

<sup>•</sup> *clk1*—mipi\_clk

- clk2—mipi\_dphy\_rx\_clk\_CLKOUT

- clk3—mipi\_dphy\_tx\_SLOWCLK

<sup>&</sup>lt;sup>(4)</sup> Using default parameter settings.

<sup>&</sup>lt;sup>(5)</sup> Using Verilog HDL.

# MIPI D-PHY TX Controller Testbench

**i**

**Note:** Contact Efinix support for MIPI D-PHY TX Controller core simulation testbench.

## **Revision History**

Table 8: Revision History

| Date          | Version | Description                                                                                                                                                                                           |

|---------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| June 2023     | 1.4     | Added Device Support and release notes sections. (DOC-1234)                                                                                                                                           |

|               |         | Updated supported data rate. (DOC-1217)                                                                                                                                                               |

|               |         | Updated HS BYTECLK and CLOCK_FREQ_MHZ parameter.                                                                                                                                                      |

|               |         | Editorial changes.                                                                                                                                                                                    |

| February 2023 | 1.3     | Added note about the resource and performance values in the resource and utilization table are for guidance only.                                                                                     |

| January 2022  | 1.2     | Updated resource utilization table. (DOC-700)                                                                                                                                                         |

| October 2021  | 1.1     | Added note to state that the f <sub>MAX</sub> in Resource<br>Utilization and Performance, and Example Design<br>Implementation tables were based on default<br>parameter settings.                    |

|               |         | Updated design example target board to production<br>Titanium Ti60 F225 Development Board and updated<br>Resource Utilization and Performance, and Example<br>Design Implementation tables. (DOC-553) |

| June 2021     | 1.0     | Initial release.                                                                                                                                                                                      |