# **I<sup>2</sup>C Core User Guide**

UG-CORE-I2C-v4.4 February 2023 www.efinixinc.com

### **Contents**

| Introduction                               | 3  |

|--------------------------------------------|----|

| Features                                   | 3  |

| Resource Utilization and Performance       | 4  |

| Functional Description                     | 5  |

| Ports                                      | 6  |

| I <sup>2</sup> C Core Registers            | 8  |

| I <sup>2</sup> C Write and Read Operations | 8  |

| IP Manager                                 | 12 |

| Customizing the I <sup>2</sup> C           | 13 |

| I <sup>2</sup> C Example Design            | 14 |

| I <sup>2</sup> C Testbench                 | 17 |

| Interface Designer GPIO Block Settings     | 17 |

| Revision History                           | 18 |

### Introduction

The I<sup>2</sup>C is a two-wire, bidirectional serial bus that provides a simple, efficient method of data exchange between devices. The I<sup>2</sup>C core provides an interface between the Trion® FPGA and an I<sup>2</sup>C bus.

Use the IP Manager to select IP, customize it, and generate files. The I<sup>2</sup>C core has an interactive wizard to help you set parameters. The wizard also has options to create a testbench and/or example design targeting an Efinix® development board.

### **Features**

- Supports native user interface

- Master, slave, and multi-master operations

- Supports 100 kHz and 400 kHz I<sup>2</sup>C operation mode

- START, Repeated START and STOP signal generation and detection

- 7-bit slave addressing mode

- Verilog HDL RTL and simulation testbench

- Includes example designs targeting the Trion® T20 BGA256 Development Board and Titanium Ti60 F225 Development Board

- Supports SDA and SCL spike filtering, and SCL clock stretching

#### **FPGA Support**

The I<sup>2</sup>C core supports all Trion® and Titanium FPGAs.

# Resource Utilization and Performance

Note: The resources and performance values provided are just guidance and change depending on the device resource utilization, design congestion, and user design.

#### Titanium Resource Utilization and Performance

| FPGA         | Mode   | Logic and<br>Adders | Flip-flops | Memory<br>Blocks | DSP48<br>Blocks | f <sub>MAX</sub><br>(MHz) <sup>(1)</sup> | Efinity <sup>®</sup><br>Version <sup>(2)</sup> |

|--------------|--------|---------------------|------------|------------------|-----------------|------------------------------------------|------------------------------------------------|

| Ti60 F225 C4 | Master | 217                 | 175        | 0                | 0               | 561                                      | 2021.2                                         |

|              | Slave  | 216                 | 175        | 0                | 0               | 438                                      |                                                |

#### Trion Resource Utilization and Performance

| FPGA          | Mode   | Logic<br>Utilization<br>(LUTs) | Registers | Memory<br>Blocks | Multipliers | f <sub>MAX</sub><br>(MHz) <sup>(1)</sup> | Efinity <sup>®</sup><br>Version <sup>(2)</sup> |

|---------------|--------|--------------------------------|-----------|------------------|-------------|------------------------------------------|------------------------------------------------|

| T20 BGA256 C4 | Master | 441                            | 203       | 0                | 0           | 154                                      | 2021.1                                         |

|               | Slave  | 258                            | 198       | 0                | 0           | 210                                      |                                                |

Using default parameter settings.

Using Verilog HDL.

### **Functional Description**

The core supports master and slave modes.

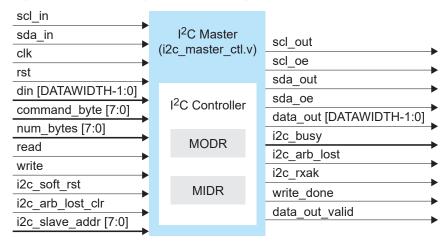

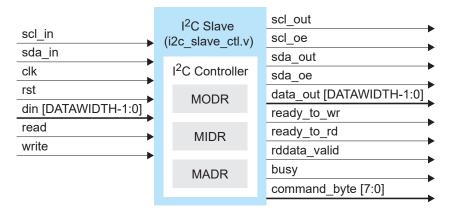

The I<sup>2</sup>C core consists of:

- $I^2C$  master—Top module wrapper that predefines the  $I^2C$  core to master mode.

- $I^2C$  slave—Top module wrapper that predefines the  $I^2C$  core to slave mode.

- *I*<sup>2</sup>*C* master/slave controller—I<sup>2</sup>*C* core logic.

- Microcontroller inbound data register (MIDR)—TX data register.

- Microcontroller outbound data register (MODR)—RX data register.

- Microcontroller address data register (MADR)—I<sup>2</sup>C slave address register.

Figure 1: I<sup>2</sup>C Master System Block Diagram

Figure 2: I<sup>2</sup>C Slave System Block Diagram

### Ports

Table 1: I<sup>2</sup>C Master Ports

| Port                      | Interface        | Direction | Description                                                                                                                                    |  |  |

|---------------------------|------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| scl_in                    | I <sup>2</sup> C | Input     | I <sup>2</sup> C clock input.                                                                                                                  |  |  |

| sda_in                    | I <sup>2</sup> C | Input     | I <sup>2</sup> C data input.                                                                                                                   |  |  |

| scl_out                   | I <sup>2</sup> C | Output    | I <sup>2</sup> C clock output.                                                                                                                 |  |  |

| scl_oe                    | I <sup>2</sup> C | Output    | I <sup>2</sup> C clock output enable.                                                                                                          |  |  |

| sda_out                   | I <sup>2</sup> C | Output    | I <sup>2</sup> C data output.                                                                                                                  |  |  |

| sda_oe                    | I <sup>2</sup> C | Output    | I <sup>2</sup> C data output enable.                                                                                                           |  |  |

| clk                       | System           | Input     | IP clock.                                                                                                                                      |  |  |

| rst                       | System           | Input     | IP reset.                                                                                                                                      |  |  |

| din [DATA_WIDTH-1:0]      | System           | Input     | Write data input.                                                                                                                              |  |  |

| command_byte [7:0]        | System           | Input     | This 8-bit data is sent to the I <sup>2</sup> C slave device during the I <sup>2</sup> C command phase.                                        |  |  |

| num_bytes [7:0]           | System           | Input     | Determines the number of data in bytes to be written to the I <sup>2</sup> C slave device or read back from the I <sup>2</sup> C slave device. |  |  |

| read                      | System           | Input     | Assert high for one clock cycle to read data from the I <sup>2</sup> C slave device.                                                           |  |  |

|                           |                  |           | Assign num_bytes before asserting the read port.                                                                                               |  |  |

| write                     | System           | Input     | Assert high for one clock cycle to write data to the I <sup>2</sup> C slave device.                                                            |  |  |

|                           |                  |           | Assign num_bytes, command_bytes, and din before asserting the write port.                                                                      |  |  |

| i2c_soft_rst              | System           | Input     | Soft reset the I <sup>2</sup> C bus.                                                                                                           |  |  |

| i2c_arb_lost_clr          | System           | Input     | Assert high for one clock cycle to clear the i2c_arb_lost port.                                                                                |  |  |

| i2c_slave_addr [7:0]      | System           | Input     | This 8-bit data is sent to the I <sup>2</sup> C slave device during the I <sup>2</sup> C header phase.                                         |  |  |

|                           |                  |           | The least significant bit is ignored.                                                                                                          |  |  |

| data_out [DATA_WIDTH-1:0] | System           | Output    | Read data output.                                                                                                                              |  |  |

| i2c_busy                  | System           | Output    | Logic high indicates that the I <sup>2</sup> C bus is busy.                                                                                    |  |  |

| i2c_arb_lost              | System           | Output    | Logic high indicates that there is arbitration lo in the $I^2$ C transfer.                                                                     |  |  |

| i2c_rxak                  | System           | Output    | Logic low indicates that the I <sup>2</sup> C slave device received and acknowledged the I <sup>2</sup> C transfer.                            |  |  |

| write_done                | System           | Output    | Logic high indicates that I <sup>2</sup> C master write data is sent and ready to accept by I <sup>2</sup> C slave device.                     |  |  |

| data_out_valid            | System           | Output    | Logic high indicates that I <sup>2</sup> C master read data is valid and ready to read by user.                                                |  |  |

### Table 2: I<sup>2</sup>C Slave Ports

| Port                      | Interface        | Direction | Description                                                                                                                                           |  |

|---------------------------|------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| scl_in                    | I <sup>2</sup> C | Input     | I <sup>2</sup> C clock input.                                                                                                                         |  |

| sda_in                    | I <sup>2</sup> C | Input     | I <sup>2</sup> C data input.                                                                                                                          |  |

| scl_out                   | I <sup>2</sup> C | Output    | I <sup>2</sup> C clock output.                                                                                                                        |  |

| scl_oe                    | I <sup>2</sup> C | Output    | I <sup>2</sup> C clock output enable.                                                                                                                 |  |

| sda_out                   | I <sup>2</sup> C | Output    | I <sup>2</sup> C data output.                                                                                                                         |  |

| sda_oe                    | I <sup>2</sup> C | Output    | I <sup>2</sup> C data output enable.                                                                                                                  |  |

| clk                       | System           | Input     | IP clock.                                                                                                                                             |  |

| rst                       | System           | Input     | IP reset.                                                                                                                                             |  |

| din [DATA_WIDTH-1:0]      | System           | Input     | Write data input.                                                                                                                                     |  |

| read                      | System           | Input     | Assert high for one clock cycle to read data from the I <sup>2</sup> C master.                                                                        |  |

| write                     | System           | Input     | Assert high for one clock cycle to write data to the I <sup>2</sup> C master. Number of data bytes to be sent to the master is equal to DATA_WIDTH/8. |  |

| data_out [DATA_WIDTH-1:0] | System           | Output    | Read data output.                                                                                                                                     |  |

| ready_to_wr               | System           | Output    | Logic high indicates that the slave is ready to accept write data from the user.                                                                      |  |

| ready_to_rd               | System           | Output    | Logic high indicates that the slave has read data ready to be read.                                                                                   |  |

| rddata_valid              | System           | Output    | Logic high indicates that the read data is valid and ready to be read by the user.                                                                    |  |

| busy                      | System           | Output    | Logic high indicates the is busy.                                                                                                                     |  |

| command_bytes [7:0]       | System           | Output    | This 8-bit data is received from I <sup>2</sup> C master device during the I2C command phase.                                                         |  |

## I<sup>2</sup>C Core Registers

Table 3: I<sup>2</sup>C Core Registers

| Bit | Name | Description                                                                                                                                                                                                                                                |

|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0 | MIDR | Data byte from command_byte and din ports are written into this data register and transferred out through the I <sup>2</sup> C bus.                                                                                                                        |

|     |      | When num_bytes is more than 2, the subsequent byte of din is written to MIDR after one byte of data transfer completed.                                                                                                                                    |

| 7:0 | MODR | Data received from the I <sup>2</sup> C transfer is written to this register. This register value is assigned to the data_out port.                                                                                                                        |

|     |      | When there are more than 1 byte of data received, the previous data byte is right-shifted to the least significant bit (LSB) and concatenate with the current received byte to form data_out.                                                              |

| 7:0 | MADR | This is an I <sup>2</sup> C slave specific register. Parameter SLAVE_ADDR is assigned to this register.                                                                                                                                                    |

|     |      | This register value is compared with the I <sup>2</sup> C header byte send by the I <sup>2</sup> C master. If these values match, the I <sup>2</sup> C slave sends ACK the I <sup>2</sup> C master. Otherwise, it sends NACK to the <sup>2</sup> C master. |

|     |      | The least significant bit is ignored. Only MADR [7:1] are compared with the header byte.                                                                                                                                                                   |

# I<sup>2</sup>C Write and Read Operations

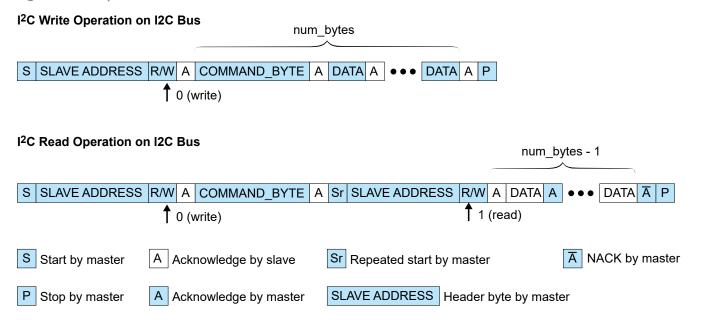

Figure 3:  $I^2C$  Operations on  $I^2C$  Bus

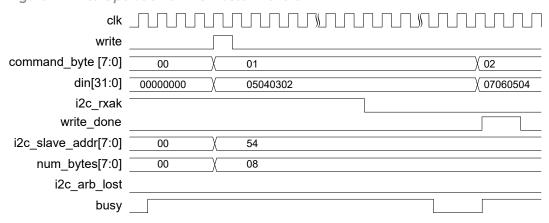

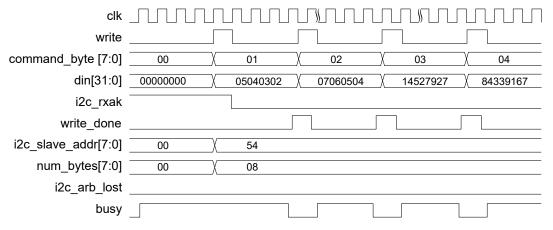

### Performing a Write Operation on I<sup>2</sup>C Master

- 1. Ensure the busy signal is low.

- 2. Assign din, command\_byte, i2c\_slave\_addr and num\_bytes, then assert the write signal for one clock cycle.

- 3. Verify the status of the busy signal. If asserted, the I<sup>2</sup>C master sends out the write data to the I<sup>2</sup>C slave device.

- 4. Verify the status of the write\_done signal. If asserted, the din is written completely. If you want to issue multiple I<sub>2</sub>C write, insert new din value after write done is high.

- 5. After the busy signal goes low, verify i2c arb lost and i2c rxak signals are low.

- **6.** The write data successfully sent out.

Figure 4: Write Operation on I<sup>2</sup>C Master Waveform

Figure 5: Multiple Write Operation on I<sup>2</sup>C Master Waveform

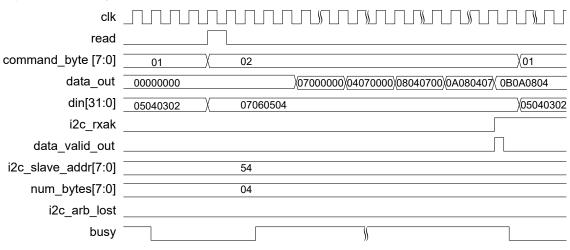

### Performing a Read Operation on I<sup>2</sup>C Master

- 1. Ensure the busy signal is low.

- 2. Assign command\_byte,i2c\_slave\_addr and num\_bytes, then assert the read signal for one clock cycle.

- 3. Verify the status of the busy signal. If asserted, the  $I^2C$  master reads from the command byte value of the  $I^2C$  slave device.

- 4. When data out valid signal is asserted, the data out is a valid read data.

- 5. After the busy signal is low, verify the i2c\_arb\_lost signal is low, and the i2c rxak signal is high.

Figure 6: Read Operation on I<sup>2</sup>C Master Waveform

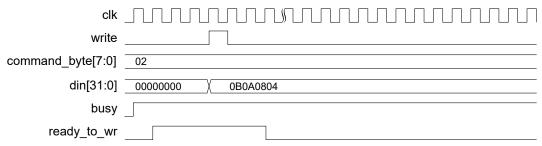

### Performing a Write Operation on I<sup>2</sup>C Slave

- 1. To send the data back to the I<sup>2</sup>C master, you must provide the write data based on the command byte value received.

- 2. Wait for the ready\_to\_wr signal to go high, then assert the write signal for one clock cycle.

- 3. Verify the status of the busy signal. If asserted, the  $I^2C$  slave sends out the write data to the  $I^2C$  master.

- 4. Verify the status of the busy signal. The write transfer is complete when the busy signal is low.

Figure 7: Write Operation on I<sup>2</sup>C Slave Waveform

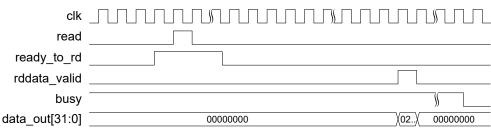

### Performing a Read Operation on I<sup>2</sup>C Slave

- 1. Wait for the ready\_to\_rd signal to go high, then assert the read signal for one clock cycle.

- 2. Verify the status of the busy signal. If asserted, the  $I^2C$  slave reads out the data transferred by the  $I^2C$  master.

- 3. Verify the status of the rddata\_valid signal. If asserted, the data\_out is a valid read data.

- 4. Verify the status of the busy signal. The read transfer is complete when the busy signal is low.

**Note:** The  $I^2C$  slave drops the additional byte if the  $I^2C$  master sends more than DATA\_BYTE\_WIDTH/8 bytes of data.

Figure 8: Read Operation on I<sup>2</sup>C Slave Waveform

### IP Manager

The Efinity® IP Manager is an interactive wizard that helps you customize and generate Efinix® IP cores. The IP Manager performs validation checks on the parameters you set to ensure that your selections are valid. When you generate the IP core, you can optionally generate an example design targeting an Efinix development board and/or a testbench. This wizard is helpful in situations in which you use several IP cores, multiple instances of an IP core with different parameters, or the same IP core for different projects.

Note: Not all Efinix IP cores include an example design or a testbench.

#### Generating a Core with the IP Manager

The following steps explain how to customize an IP core with the IP Configuration wizard.

- 1. Open the IP Catalog.

- 2. Choose an IP core and click Next. The IP Configuration wizard opens.

- 3. Enter the module name in the Module Name box.

**Note:** You cannot generate the core without a module name.

- **4.** Customize the IP core using the options shown in the wizard. For detailed information on the options, refer to the IP core's user guide or on-line help.

- 5. (Optional) In the **Deliverables** tab, specify whether to generate an IP core example design targeting an Efinix® development board and/or testbench. For SoCs, you can also optionally generate embedded software example code. These options are turned on by default.

- **6.** (Optional) In the **Summary** tab, review your selections.

- 7. Click Generate to generate the IP core and other selected deliverables.

- **8.** In the **Review configuration generation** dialog box, click **Generate**. The Console in the **Summary** tab shows the generation status.

**Note:** You can disable the **Review configuration generation** dialog box by turning off the **Show Confirmation Box** option in the wizard.

9. When generation finishes, the wizard displays the **Generation Success** dialog box. Click **OK** to close the wizard.

The wizard adds the IP to your project and displays it under IP in the Project pane.

#### Generated Files

The IP Manager generates these files and directories:

- <module name>\_define.vh—Contains the customized parameters.

- <module name>\_tmpl.v—Verilog HDL instantiation template.

- <module name>\_tmpl.vhd—VHDL instantiation template.

- <module name>.v—IP source code.

- settings.json—Configuration file.

- **<kit name>\_devkit**—Has generated RTL, example design, and Efinity® project targeting a specific development board.

- **Testbench**—Contains generated RTL and testbench files.

**Note:** Refer to the IP Manager chapter of the Efinity® Software User Guide for more information about the Efinity® IP Manager.

# Customizing the I<sup>2</sup>C

The core has parameters so you can customize its function. You set the parameters in the General tab of the core's IP Configuration window.

Table 4: I<sup>2</sup>C Core Master Parameters when I2C Controller Mode is MASTER

| Parameters                    | Options                                      | Description                                                                                                                  |

|-------------------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

| I2C Data Transfer Speed       | 100 kHz normal<br>mode, 400<br>kHz fast mode | I <sup>2</sup> C data transfer speed.  Default = 100 kHz normal mode                                                         |

| Data Width                    | 8, 16, 24, 32                                | Data width for the user interface data input/output bus.  Default = 32                                                       |

| Core Clock Frequency (MHz)    | 50, 100, 150                                 | Core clock frequency. Default = 100                                                                                          |

| SDA/SCL Spike Filtering Cycle | 1 - 15                                       | SDA/SCL spike filtering logic to filter out signal spike in clock cycle with reference to core clock frequency.  Default = 2 |

Table 5: I<sup>2</sup>C Core Master Parameters when I2C Controller Mode is Slave

| Parameters                    | Range         | Description                                                                                                     |

|-------------------------------|---------------|-----------------------------------------------------------------------------------------------------------------|

| 8-bit I2C Slave Address       | _             | Slave address for the I <sup>2</sup> C slave.                                                                   |

|                               |               | The least significant bit is ignored.                                                                           |

|                               |               | Default = 84 (decimal)                                                                                          |

| I2C Data Transfer Speed       | 0, 1          | I <sup>2</sup> C data transfer speed.                                                                           |

|                               |               | Default = 100 kHz normal mode                                                                                   |

| Data Width                    | 8, 16, 24, 32 | Data width for the user interface data input/output bus.                                                        |

|                               |               | Default = 32                                                                                                    |

| Core Clock Frequency (MHz)    | 50, 100, 150  | Core clock frequency in MHz.                                                                                    |

|                               |               | Default = 100                                                                                                   |

| SDA/SCL Spike Filtering Cycle | 1 - 15        | SDA/SCL spike filtering logic to filter out signal spike in clock cycle with reference to core clock frequency. |

|                               |               | Default = 2                                                                                                     |

# I<sup>2</sup>C Example Design

You can choose to generate the example design when generating the core in the IP Manager Configuration window. Compile the example design project and download the .hex or .bit file to your board.

(!)

Important: Efinix tested the example design generated with the default parameter options only.

The example designs the target the Trion® T20 BGA256 Development Board and Titanium Ti60 F225 Development Board.

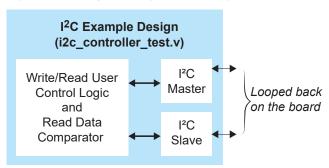

Figure 9: Example Design Block Diagram

The example design flow consists of the following steps:

- 1. The user control logic asserts the write signal with din, command\_byte, and num bytes assigned to the I<sup>2</sup>C master.

- 2. The I<sup>2</sup>C master sends data to the I<sup>2</sup>C slave, once complete, the user control logic asserts write done signal.

- 3. Once the ready\_to\_rd signal is high, the user control logic asserts the read signal to the I<sup>2</sup>C slave and start receiving the data from I<sup>2</sup>C master.

- **4.** Once the rddata\_valid signal is high, the user control logic compares the read data from the I<sup>2</sup>C slave with the write data written from I<sup>2</sup>C master.

- 5. The user control logic asserts the read signal with command\_byte and num\_bytes assigned to the  $I^2C$  master.

- **6.** The  $I^2C$  master sends command byte to the  $I^2C$  slave.

- 7. Once the ready\_to wr signal is high, the user control logic asserts the write signal with din to the  $I^2C$  slave.

- **8.** The I2C slave sends data to the  $I^2$ C master.

- 9. Once the data\_out\_valid signal is high, the user control logic compares the read data from the I<sup>2</sup>C master with the write data written from I<sup>2</sup>C slave.

- 10. Once the busy signal is low, the example design operation is completed.

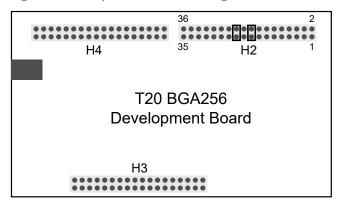

#### Trion® T20 BGA256 Development Board

External jumpers are required to connect the I<sup>2</sup>C SDA and SCL ports between master and slave at the Trion® T20 BGA256 Development Board. The following table describes the external jumper requirements for the example design.

Table 6: External Jumper for Trion® T20 BGA256 Development Board

| Connection Port | Header | Jumper Setting         |  |  |

|-----------------|--------|------------------------|--|--|

| SDA H2          |        | Connect pins 17 and 18 |  |  |

| SCL             | H2     | Connect pins 21 and 22 |  |  |

Figure 10: Jumper Connection Diagram

The LED displays the first data byte that the slave or master receive sequentially from LED D3, D4, D5 and D6 continuously.

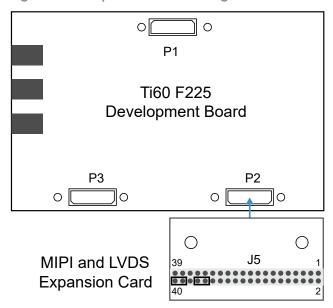

#### Titanium Ti60 F225 Development Board

External jumpers are required to connect the I<sup>2</sup>C SDA and SCL ports between master and slave at the Titanium Ti60 F225 Development Board through the MIPI and LVDS Expansion Daughter Card. Connect the P3 header of the daughter card to the P2 header of the Titanium Ti60 F225 Development Board.

The following table describes the external jumper requirements at the MIPI and LVDS Expansion Daughter Card for the example design.

Table 7: External Jumper for MIPI and LVDS Expansion Daughter Card

| Connection Port Header Jumper Setting |    |                        |

|---------------------------------------|----|------------------------|

| SDA                                   | J5 | Connect pins 32 and 34 |

| SCL                                   | J5 | Connect pins 38 and 40 |

Figure 11: Jumper Connection Diagram

The LED displays the first data byte that the slave or master received in sequentially from LEDs D16 green and LED D17 white to LED D16 red and LED D17 yellow continuously.

Table 8: Trion® Example Design Implementation

| FPGA          | Mode   | Logic<br>Utilization<br>(LUTs) | Registers | Memory<br>Blocks | Multipliers | f <sub>MAX</sub><br>(MHz) <sup>(3)</sup> | Efinity <sup>®</sup><br>Version <sup>(4)</sup> |

|---------------|--------|--------------------------------|-----------|------------------|-------------|------------------------------------------|------------------------------------------------|

| T20 BGA256 C4 | Master | 723                            | 414       | 0                | 0           | 95                                       | 2021.1                                         |

|               | Slave  | 722                            | 414       | 0                | 0           | 93                                       |                                                |

Table 9: Titanium Example Design Implementation

| FPGA         | Mode   | Logic and<br>Adders | Flip-flops | Memory<br>Blocks | DSP48<br>Blocks | f <sub>MAX</sub><br>(MHz) <sup>(3)</sup> | Efinity <sup>®</sup><br>Version <sup>(4)</sup> |

|--------------|--------|---------------------|------------|------------------|-----------------|------------------------------------------|------------------------------------------------|

| Ti60 F225 C4 | Master | 703                 | 414        | 0                | 0               | 332                                      | 2021.2                                         |

|              | Slave  | 700                 | 414        | 0                | 0               | 339                                      |                                                |

Using default parameter settings.

(4) Using Verilog HDL.

# I<sup>2</sup>C Testbench

You can choose to generate the testbench when generating the core in the IP Manager Configuration window.

Note: You must include all .v files generated in the /testbench directory in your simulation.

Efinix provides a simulation script for you to run the testbench quickly using the Modelsim software. To run the Modelsim testbench script, run vsim -do modelsim.do in a terminal application. You must have Modelsim installed in your computer to use this script.

The testbench provides read and write tests. Each test case indicates a pass or fail results for the register read/write tests. After running the simulation, the test prints the following message indicating the pass/fail results:

```

Slave received the command byte from Master 01 Slave received the data byte from Master 040302 Slave received the command byte from Master 02 Slave received the data byte from Master 060504 Master received the data byte from Slave, 4

```

**Note:** If you want to use your own testbench file, add the following line in your testbench file, *instancename\_tb.v*:

`define SIM

### Interface Designer GPIO Block Settings

The I<sup>2</sup>C SCL and SDA are bidirectional ports. When using the I<sup>2</sup>C core to communicate with I<sup>2</sup>C devices outside of the Trion® FPGA, set the GPIO block as follows:

- 1. In the Interface Designer, create a new GPIO block.

- 2. In the GPIO Block Editor, set the Mode to inout.

- 3. Select weak pullup in the Pull Option drop-down list.

# Revision History

Table 10: Revision History

| Date           | Version | Description                                                                                                                                                                                    |

|----------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| February 2023  | 4.4     | Added note about the resource and performance values in the resource and utilization table are for guidance only.                                                                              |

| January 2022   | 4.3     | Updated resource utilization table. (DOC-700)                                                                                                                                                  |

| October 2021   | 4.2     | Added note to state that the f <sub>MAX</sub> in Resource Utilization and Performance, and Example Design Implementation tables were based on default parameter settings.                      |

|                |         | Updated design example target board to production Titanium Ti60 F225 Development Board and updated Resource Utilization and Performance, and Example Design Implementation tables. (DOC-553)   |

| September 2021 | 4.1     | Removed num_bytes [7:0] port possible values limitation.                                                                                                                                       |

| June 2021      | 4.0     | Added note about including all $.v$ generated in testbench folder is required for simulation.                                                                                                  |

|                |         | Added write_done, data_out_valid, and slv_command_byte ports.                                                                                                                                  |

|                |         | Updated resource utilization and performance table.                                                                                                                                            |

|                |         | Updated example design output and implementation table.                                                                                                                                        |

|                |         | Added support for Titanium FPGAs and example design for Titanium Ti60 F225 Development Board.                                                                                                  |

|                |         | Added multiple write on master waveform.                                                                                                                                                       |

|                |         | Updated for Efinity v2021.1.                                                                                                                                                                   |

| December 2020  | 3.0     | Added busy signal to the I <sup>2</sup> C slave controller.                                                                                                                                    |

|                |         | Updated core name to I <sup>2</sup> C core.                                                                                                                                                    |

|                |         | Updated user guide for Efinix® IP Manager which includes added IP Manager topics, updated parameters, and user guide structure.                                                                |

| July 2020      | 2.0     | Updated for I <sup>2</sup> C Master/Slave Controller core v2.0.                                                                                                                                |

|                |         | Added support for SDA and SCL spike filtering and SCL clock stretching.                                                                                                                        |

|                |         | Updated LUTs utilization for master and slave mode in resource utilization and performance.                                                                                                    |

|                |         | Added MASTER_I2C_FAST_MODE, MASTER_CLOCK_FREQ, MASTER_SPIKE_FILTER_CYCLE, SLAVE_I2C_FAST_MODE, SLAVE_CLOCK_FREQ, and SLAVE_SPIKE_FILTER_CYCLE parameters.                                      |

|                |         | Updated LUTs and f <sub>MAX</sub> in example design implementation.                                                                                                                            |

|                |         | Updated example design block diagram to remove clock divider block. I <sup>2</sup> C I2C core v2.0 supports core clock frequency of 150 Mhz and 100 Mhz and clock divider is no longer needed. |

| May 2020       | 1.0     | Initial release.                                                                                                                                                                               |

| 2              |         |                                                                                                                                                                                                |