![]()

Open Source

![]()

Field Reconfigurable

![]()

Free AI Framework

![]()

High Performance and Low Power

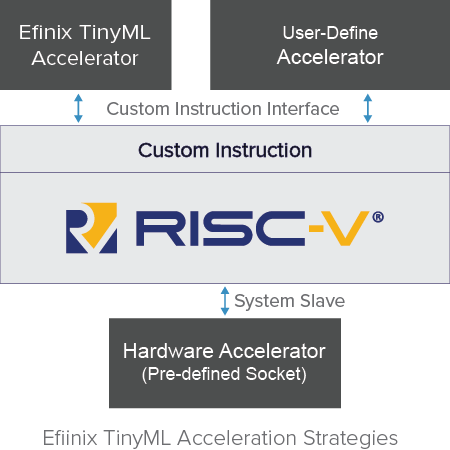

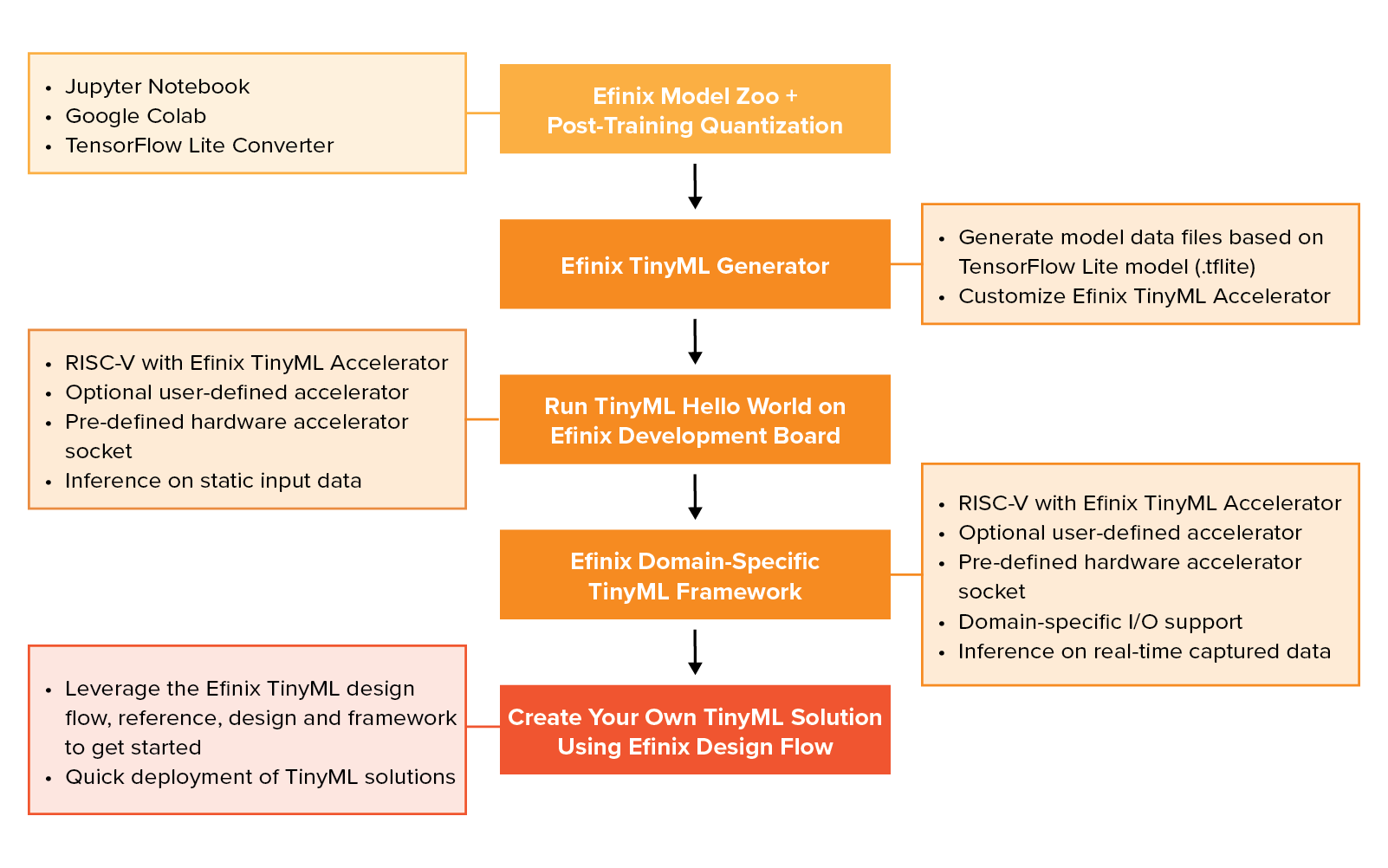

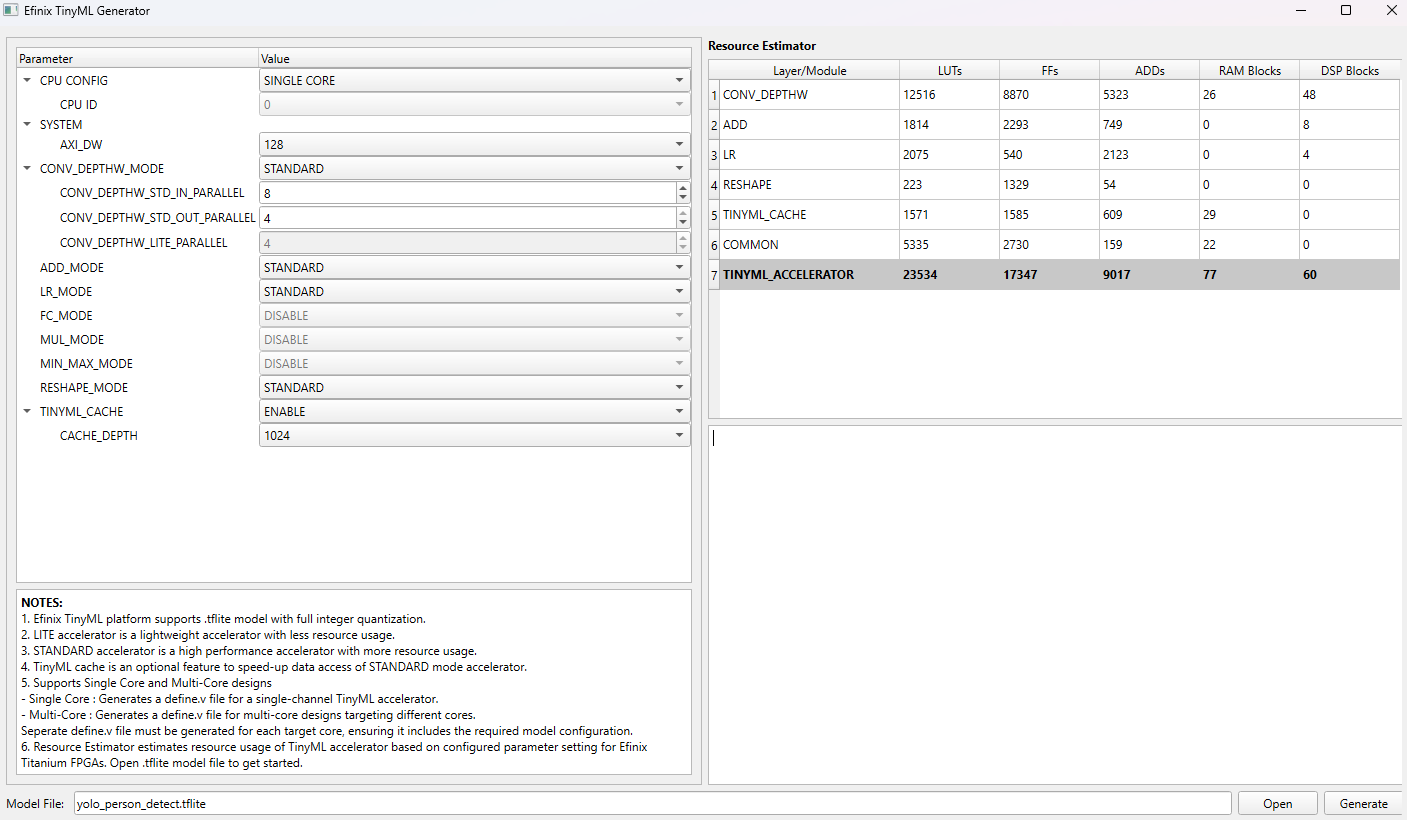

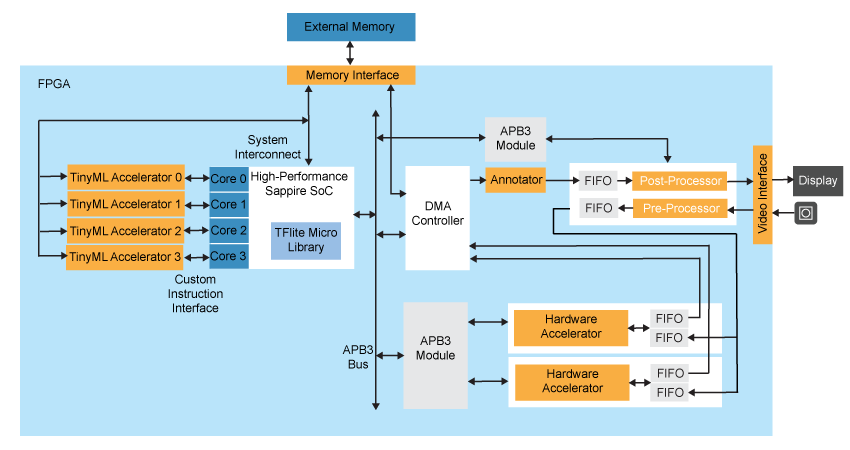

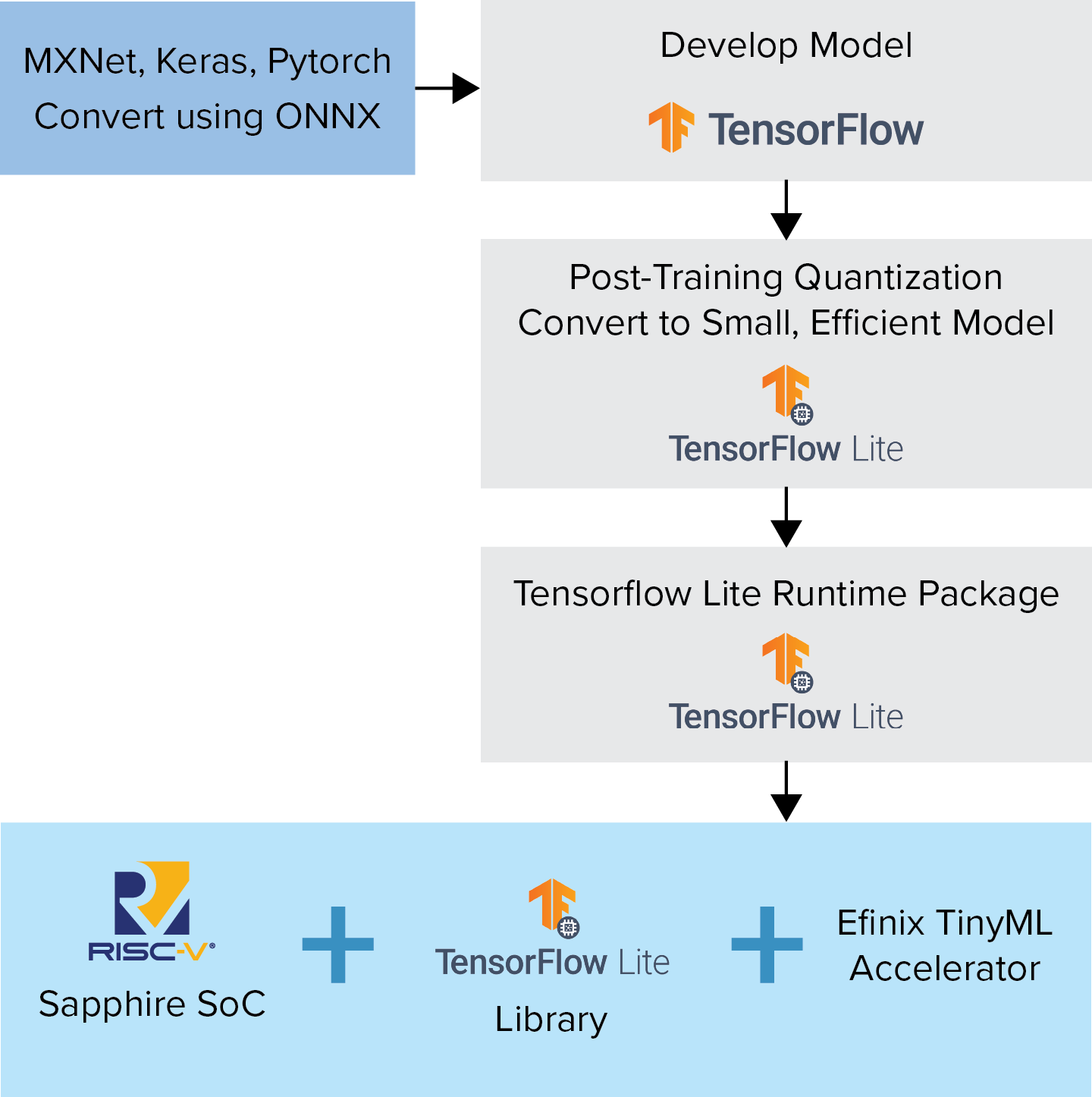

人工知能(AI)をネットワークエッジに近づけ、低レイテンシでコンテキストを増やしながらデータを処理できるようにする動きがあります。しかし、エッジでは電力と計算リソースが貴重であり、計算リソースを大幅に消費するAIアルゴリズムでは。必要なパフォーマンスを実現することが困難です。オープンソースコミュニティは、標準のTensorFlowモデルの量子化バージョンを作成し、関数のライブラリを使用して、それらを終端のマイクロコントローラで実行できるようにするTensorFlow Liteを開発しました。Efinix TinyMLプラットフォームは、これらのTensorFlow Liteモデルを取得し、Sapphireコアのカスタム命令機能を使用して、FPGAハードウェアでそれらを高速化し、低消費電力と小さなフットプリントを維持しながらパフォーマンスを大幅に向上させます。

Efinix TinyMLプラットフォームの利点

- 構成可能なSapphire SoC スイート、Efinix TinyMLアクセラレータ、オプションのユーザー定義アクセラレータ、ハードウェアアクセラレータソケットを備えた柔軟なAIソリューションで、さまざまなアプリケーションのニーズに対応します。

- オープンソース コミュニティによって管理されている TFLite Micro ライブラリでサポートされているすべての AI推論をサポートします。

- パフォーマンスと設計効率の比率が異なる複数のアクセラレーション オプションにより、AI推論デプロイメントを迅速にします。

TensorFlow, the TensorFlow logo and any related marks are trademarks of Google Inc.