# **AN 006: Configuring Trion**<sup>®</sup> **FPGAs**

AN006-v6.0 February 2024 www.efinixinc.com

# **Contents**

| About Configuring Trion <sup>®</sup> FPGAs                         | 4  |

|--------------------------------------------------------------------|----|

| Bitstream Size                                                     |    |

| Configuration Time                                                 |    |

| Planning Your Device Pinout                                        |    |

| Other Factors to Consider                                          | č  |

| Configuration Pins                                                 |    |

| FPGA Configuration Modes                                           | 10 |

| Selecting the Configuration Mode                                   |    |

| About SPI Clocking and Sampling                                    |    |

| SPI Active Mode                                                    |    |

| SPI Active Mode for SIP Packages                                   |    |

| SPI Active Mode without CSI                                        |    |

| Clocking                                                           |    |

| SPI Passive ModeSPI Passive Mode without CSI or CBUS2              |    |

| JTAG Mode                                                          |    |

|                                                                    |    |

| Flash Programming Modes  Programming the Flash Using a JTAG Bridge |    |

|                                                                    |    |

| Power Up                                                           |    |

| Power Up Sequence                                                  |    |

| Power Supply Current TransientPower Up Circuitry Recommendation    |    |

|                                                                    |    |

| Configuration Sequence                                             | 30 |

| Support for Multiple Images                                        | 31 |

| Configuring Multiple FPGAs                                         | 33 |

| Daisy Chaining with a SPI Flash Device                             |    |

| Daisy Chaining with a Microcontroller or Microprocessor            |    |

| Resistors in Configuration Circuitry                               |    |

| Configuration Timing                                               |    |

|                                                                    |    |

| Selecting the Right SPI Flash Device                               | 39 |

| Supported Flash Devices                                            | 39 |

| Connecting Programming Hardware                                    | 40 |

| SPI Programming Connections                                        |    |

| JTAG Programming Connections                                       | 41 |

| Using the Efinity Programmer                                       | 43 |

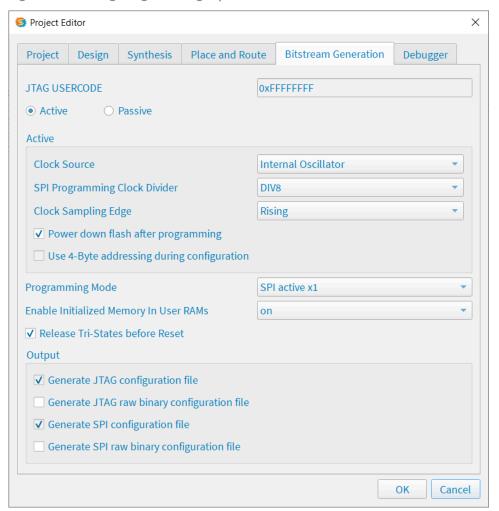

| Generate a Bitstream (Programming) File                            | 43 |

| Working with Bitstreams                                            |    |

| Edit the Bitstream Header                                          |    |

| Export to Raw Binary Format                                        |    |

| Export to .svf Format                                              |    |

| Convert to Intel Hex Format at the Command Line                    |    |

| Combine distreams and Other files                                  | 40 |

|            | SPI Programming                                    | 46 |

|------------|----------------------------------------------------|----|

|            | Program a Single Image                             |    |

|            | Program Multiple Images (CBSEL)                    |    |

|            | Program Multiple Images (Internal Reconfiguration) | 47 |

|            | Program Multiple Images (Bitstream and Data)       |    |

|            | Program a Daisy Chain                              |    |

|            | JTAG Programming                                   |    |

|            | JTAG Device IDs                                    |    |

|            | Program a Single Image                             |    |

|            | Program Using a JTAG Chain                         |    |

|            | Program using a JTAG Bridge (New)                  |    |

|            | Program using a JTAG Bridge (Legacy)               |    |

|            | JTAG Programming with FTDI Chip Hardware           |    |

|            | FDTI Programming at the Command Line               |    |

|            | Using the Command-Line Programmer                  |    |

|            | Project-Based Programming Options                  |    |

| Ve         | erifying Configuration                             | 58 |

|            | stalling USB Drivers                               |    |

|            | Installing the Linux USB Driver                    |    |

|            | Installing the Windows USB Driver                  |    |

| <b>n</b> - | evision History                                    | 62 |

| K F        | 2VISION MISTORY                                    |    |

# About Configuring Trion® FPGAs

This document describes how to configure Trion® FPGAs. These FPGAs contain volatile Configuration RAM (CRAM) that you must configure with the desired logic function (via a bitstream) upon power-up and before the core enters normal operation. The Efinity® software generates the bitstream, which is design dependent.

Learn more: Refer to the Efinity Software User Guide for information on how to generate the bitstream.

### Bitstream Size

The bitstream size is dependent on the FPGA you choose and the configuration parameters you set in the Efinity software.

**Note:** In the Efinity software, you can optionally add header information to the bitstream file. This header information can add up to 1k bytes to the configuration size. The following maximums include the optional header size.

Table 1: Trion® FPGA Bitstream Size

| FPGA | Maximum Supported Configuration Bits (Single Image) | Packages                             |

|------|-----------------------------------------------------|--------------------------------------|

| T4   | 1,348,184                                           | All                                  |

| T8   | 1,394,584                                           | BGA49, BGA81                         |

|      | 5,255,968                                           | QFP144                               |

| T13  | 5,261,920                                           | All                                  |

| T20  | 5,255,968                                           | QFP144                               |

|      | 5,445,600                                           | WLCSP80, QFP100F3,<br>BGA169, BGA256 |

|      | 8,003,744                                           | BGA324, BGA400                       |

| T35  | 8,139,168                                           | All                                  |

| T55  | 27,675,040                                          | All                                  |

| T85  | 28,042,400                                          | All                                  |

| T120 | 28,409,760                                          | All                                  |

# **Configuration Time**

The FPGA configuration time depends on the frequency and data bus width. To estimate the configuration time for a given FPGA, use the following equation:

Configuration time = bitstream size / (configuration clock frequency \* data bus width)

**Note:** The maximum configuration clock frequency depends on the configuration mode and implementation.

#### For example:

- T8 FPGA—approximately 1.38 Mbits of configuration data:

- Configuration clock frequency—10 MHz

- T8 Configuration data bus width—8 bits

Configuration time: 1.38 Mbits \* 100 ns / 8 = 17.25 ms

# Planning Your Device Pinout

The configuration mode you choose affects your design's pinout. You should decide which mode you will use and plan for it before performing floorplanning or pin selection for your logic design.

Active and passive configuration modes use multi-function pins during configuration. When configuration completes, these multi-function pins are available for general use. JTAG configuration uses dedicated configuration pins that cannot be used for other functions. Additionally, the configuration mode you choose can affect the voltage restrictions for the I/O bank that contains the configuration pins.

#### Efinix® recommends that you:

- Choose the configuration mode(s). Consider the primary configuration mode as well as configuration modes you may need for debugging or future updates.

- Find the pin and the bank locations for the configuration mode(s).

- Understand how you use these pins and any restrictions when using multi-function configuration pins as standard I/O pins. For example, consider internal and external pullups or pull-downs, connections to external devices, etc.

**Note:** In some situations, you may want to use a multi-function configuration pin as an output pin in user mode. If the pin is driven by an external device during configuration, the source that drives this pin during configuration must be tri-stated before the device enters user mode and user logic begins driving it. Otherwise, the drivers can be in contention, and can damage the pin.

• For each set of configuration pins, determine the common required I/O voltage support for the required configuration bank. You can only use compatible I/O standards elsewhere in that bank.

### Other Factors to Consider

Although configuration is typically a one-time event independent of device operation, your configuration choices can affect your design options. Make configuration decisions early in the design cycle to eliminate challenges later:

- Do you need to support JTAG configuration for debugging purposes?

- How can you provide easy access to the configuration control and status pins for debugging?

- What multi-function pins are you using in your logic design and are they active during configuration? If they are, check for conflicts with other uses of these pins.

#### Additionally, you should:

- Provide quality signal integrity for key signals during PCB layout, including the configuration clock (even though configuration can operate at a low frequency).

- Understand the configuration sequence to reduce configuration time.

- Generate the configuration bitstream for your FPGA using Efinity tools.

# **Configuration Pins**

Some configuration pins are dedicated, and some are dual-purpose.

- Dedicated pins cannot be used as general purpose I/O.

- During configuration, use dual-purpose pins as described in this document for the configuration mode you are using. After configuration (in user mode), you can use these pins as general-purpose I/O.

**Table 2: Dedicated Configuration Pins**

These pins cannot be used as general-purpose I/O after configuration.

All the pins are in internal weak pull-up during configuration except for TCK and TDO.

| Pins     | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | External Weak<br>Pull- Up/<br>Pull Down<br>Requirement |

|----------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| CDONE    | I/O       | Configuration done status pin. CDONE is an open drain output; connect it to an external pull-up resistor to VCCIO. When CDONE = 1, the configuration is complete and the FPGA enters user mode. You can hold CDONE low and release it to synchronize the FPGAs entering user mode.                                                                                                                                                                                           | Pull up                                                |

| CRESET_N | Input     | Active-low FPGA reset and re-configuration trigger.  Pulse CRESET_N low for a duration of t <sub>creset_N</sub> before releasing CRESET_N from low to high to initiate FPGA re-configuration. This pin does not perform a system reset.                                                                                                                                                                                                                                      | Pull up                                                |

| TCK      | Input     | JTAG test clock input (TCK). The rising edge loads signals applied at the TAP input pins (TMS and TDI). The falling edge clocks out signals through the TAP TDO pin.                                                                                                                                                                                                                                                                                                         | Pull up                                                |

| TMS      | Input     | JTAG test mode select input (TMS). The I/O sequence on this input controls the test logic operation . The signal value typically changes on the falling edge of TCK. TMS has an internal weak pull-up; when it is not driven by an external source, the test logic perceives a logic 1.                                                                                                                                                                                      | Pull up                                                |

| TDI      | Input     | JTAG test data input (TDI). Data applied at this serial input is fed into the instruction register or into a test data register depending on the sequence previously applied at TMS. Typically, the signal applied at TDI changes state following the falling edge of TCK while the registers shift in the value received on the rising edge. Like TMS, TDI has an internal weak pull-up; when it is not driven from an external source, the test logic perceives a logic 1. | Pull up                                                |

| TDO      | Output    | JTAG test data output (TDO). This serial output from the test logic is fed from the instruction register or a test data register depending on the sequence previously applied at TMS. The shift out content is based on the issued instruction. The signal driven through TDO changes state following the falling edge of TCK. When data is not being shifted through the device, TDO is set to an inactive drive state (e.g., high-impedance).                              | Pull up                                                |

Table 3: Dual-Purpose Configuration Pins

In user mode (after configuration), you can use these dual-purpose pins as general I/O.

| Pins       | Direction                                                                                                                                                                                                                                                                                                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                     | External Weak<br>Pull- Up/<br>Pull Down<br>Requirement |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| CBUS[2:0]  | Input                                                                                                                                                                                                                                                                                                      | Configuration bus width select. CBUS has an internal weak pull-<br>up. However, Efinix recommends that you use an external pull-<br>up accordingly. See <i>Selecting the Configuration Mode</i> in AN 006:<br>Configuring Trion FPGAs                                                                                                                                                                                                                           | Pull up or<br>pull down <sup>(1)</sup>                 |

| CBSEL[1:0] | Input                                                                                                                                                                                                                                                                                                      | Optional multi-image selection input (if external multi-image configuration mode is enabled).                                                                                                                                                                                                                                                                                                                                                                   | Pull up or<br>pull down <sup>(2)</sup>                 |

| ССК        | I/O                                                                                                                                                                                                                                                                                                        | Passive SPI input configuration clock or active SPI output configuration clock (active low). Includes an internal weak pull-up.  Important: The CCK pin in Q100F3 packages are only available in user mode when the LVDS TX resources are not in use. The CCK pin should not be toggled when any LVDS TX is used.                                                                                                                                               | Optional<br>pull up if<br>required by<br>external load |

| CDIn       | I/O                                                                                                                                                                                                                                                                                                        | <ul> <li>n is a number from 0 to 31 depending on the SPI configuration.</li> <li>0: Passive serial data input or active serial output.</li> <li>1: Passive serial data output or active serial input.</li> <li>n: Parallel I/O.</li> <li>In multi-bit daisy chain connection, the CDIn (31:0) connects to the data bus in parallel.</li> </ul>                                                                                                                  | Optional<br>pull up if<br>required by<br>external load |

| CSI        | Input                                                                                                                                                                                                                                                                                                      | Chip select.  0: The FPGA is not selected or enabled and will not be configured.  1: Selects the FPGA for all configuration modes.                                                                                                                                                                                                                                                                                                                              | Pull up                                                |

| CSO        | Output                                                                                                                                                                                                                                                                                                     | Chip select output. Selects the next device for cascading configuration.                                                                                                                                                                                                                                                                                                                                                                                        | N/A                                                    |

| NSTATUS    | Output Status (active low).  Indicates a configuration error. When the FPGA drives this pin low, it indicates an ID mismatch, the bitstream CRC check has failed, or remote update has failed.  For Trion® T4, T8 BGA49, and T8 BGA81 FPGAs, logic low indicates a configuration error due to ID mismatch. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | N/A                                                    |

| SS_N       | Input                                                                                                                                                                                                                                                                                                      | SPI slave select (active low). Includes an internal weak pull-up resistor to VCCIO during configuration. During configuration, the logic level samples on this pin determine the configuration mode. This pin is an input when sampled at the start of configuration (SS is low); an output in active SPI flash configuration mode. The FPGA senses the value of SS_N when it comes out of reset (pulse CRESET_N low to high).  0: Passive mode  1: Active mode |                                                        |

| TEST_N     | Input                                                                                                                                                                                                                                                                                                      | Active-low test mode enable signal. Set to 1 to disable test mode.  During all configuration modes, rely on the external weak pull-up or drive this pin high.                                                                                                                                                                                                                                                                                                   | Pull up                                                |

Optional for x1 mode.

Not applicable to single-image or remote update.

| Pins         | Direction | Description                                                                                                            | External Weak<br>Pull- Up/<br>Pull Down<br>Requirement |

|--------------|-----------|------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| RESERVED_OUT | Output    | Reserved pin during user configuration. This pin drives high during user configuration. BGA49 and BGA81 packages only. | N/A                                                    |

# FPGA Configuration Modes

Trion® FPGAs have dedicated configuration pins. You select the configuration mode by setting the appropriate condition on the input configuration pins. Trion® FPGAs support the following configuration modes.

**Table 4: FPGA Configuration Modes**

| Mode                          | Description                                                                                                       |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------|

| SPI Active (serial/parallel)  | The FPGA loads the bitstream itself from non-volatile SPI flash memory.                                           |

| SPI Passive (serial/parallel) | An external microprocessor or microcontroller sends the bitstream to the FPGA using the SPI interface.            |

| JTAG                          | A host computer sends instructions through a download cable to the FPGA's JTAG interface using JTAG instructions. |

# Selecting the Configuration Mode

Each configuration interface corresponds to one or more configuration modes and bus widths.

- Select the configuration mode by setting the appropriate condition on the CBUS [2:0], SS N, and TEST N input pins.

- Set CBUS2, CBUS1, CBUS0, SS\_N, and TEST\_N using a pull-up or pull-down resistor, or drive them with an external active device.

- Do not toggle the mode pins before the FPGA enters user mode.

**Table 5: SPI Hardware Settings**

If you do not make any connections, the default mode is x1 SPI active.

| Configuration<br>Mode | Parallel/Serial | TEST_N | SS_N | CBUS2,<br>CBUS1, CBUS0 | Width |

|-----------------------|-----------------|--------|------|------------------------|-------|

| SPI Active            | Serial          | 1      | 1    | 3'b111                 | x1    |

|                       | Parallel        | 1      | 1    | 3'b110                 | x2    |

|                       | Parallel        | 1      | 1    | 3'b101                 | x4    |

| SPI Passive           | Serial          | 1      | 0    | 3'b111                 | x1    |

|                       | Parallel        | 1      | 0    | 3'b110                 | x2    |

|                       | Parallel        | 1      | 0    | 3'b101                 | x4    |

|                       | Parallel        | 1      | 0    | 3'b100                 | x8    |

|                       | Parallel        | 1      | 0    | 3'b011                 | x16   |

|                       | Parallel        | 1      | 0    | 3'b010                 | x32   |

The JTAG/boundary-scan configuration interface is always available regardless of pin settings. If you send configuration instructions to the JTAG interface, the Trion® FPGA overwrites the previous configuration.

**Note:** You must set the configuration mode in the Efinity® software; the software includes the mode and other configuration options in the bitstream.

The supported configuration modes are FPGA specific. Refer to your FPGA's data sheet for information on the configuration modes it supports.

# About SPI Clocking and Sampling

Table 6: SPI Interface Clocking and Sampling

| Mode    | Clock                                       | Sampling Edge               |

|---------|---------------------------------------------|-----------------------------|

| Passive | The CCK clock comes from an external device | Positive                    |

| Active  | The FPGA generates the CCK clock            | Positive (not configurable) |

**Important:** Refer to the setup and hold times in the data sheet to ensure system timing closure based on your timing budget.

The microprocessor or microcontroller can set the SPI clock polarity (CPOL bit) and the clock phase (CPHA bit) when the interface is idle, which results in 4 modes, depending on how you set these bits. Use mode 3 in your microprocessor or microcontroller when programming the FPGA.

Table 7: SPI Clock Polarity and Phase Modes

| Mode | Clock Polarity<br>when Idle | Data Sampled On | Data Shifted On |

|------|-----------------------------|-----------------|-----------------|

| 0    | Low                         | Rising edge     | Falling edge    |

| 1    | Low                         | Falling edge    | Rising edge     |

| 2    | High                        | Falling edge    | Rising edge     |

| 3    | High                        | Rising edge     | Falling edge    |

Efinix uses mode 3 for SPI passive mode, which is CPOL bit = 1 and CPHA bit = 1 for all Trion FPGA devices.

**MODE** 0 1 0 1 **CPHA Bit CPOL Bit** Sample Sample (CPOL Bit, CPHA Bit) = Mode # (0,0) = Mode 00 (0,1) = Mode 1(1,0) = Mode 2(1,1) = Mode 31

Sample

3

Figure 1: SPI Clock Polarity and Phase Modes Diagram

### **SPI** Active Mode

Sample

2

**MODE**

In active mode, the FPGA loads configuration data itself from a configuration bitstream that typically resides in non-volatile memory on the same board. Active modes can be serial or parallel. The FPGA internally generates the configuration clock signal (CCK) and controls configuration by sending a clock or addresses to the flash memory.

The active SPI configuration mode supports low pin count, industry-standard external SPI flash devices to store the bitstream. The FPGA supports a direct connection to the flash device's four-pin SPI interface. Active SPI configuration mode can read from standard 1-bit serial SPI flash devices as well as from flash devices that support x2 and x4 fast output read operations. These modes are proportionally faster than the standard 1-bit SPI interface.

**Note:** Trion® FPGAs only support SPI flash memory with 3-byte addressing mode for configuration.

**Table 8: Active Mode Instructions**

| Instruction | Description           | SPI Data Width |

|-------------|-----------------------|----------------|

| 0BH         | Fast Read             | x1             |

| 3BH         | Dual Output Fast Read | x2             |

| 6BH         | Quad Output Fast Read | x4             |

The FPGA samples CBUS0, CBUS1, and CBUS2 after power-up or reconfiguration; therefore, you must drive these signals to the correct value.<sup>(3)</sup>

<sup>(3)</sup> Smaller packages may not have CBUS2 bonded out. In this case, CBUS2 is held high in the package.

#### **Connection Examples**

**Note:** A circuitry is required to control the CRESET\_N pin to meet the  $t_{CRESET\ N}$  requirement.

**Learn more:** Refer to Trion Hardware Design Checklist and Guidelines for the detailed connection requirements.

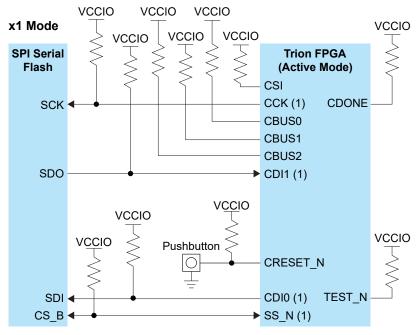

Figure 2: Active (x1)

See Resistors in Configuration Circuitry on page 37 for the resistor values.

Note:

1. The external pull-up is optional unless required by an external load.

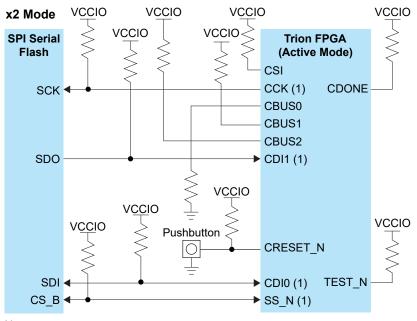

Figure 3: Active (x2)

See Resistors in Configuration Circuitry on page 37 for the resistor values.

#### Note:

1. The external pull-up is optional unless required by an external load.

**Note:** The connections for x2 are the same as x1. However:

The modes use different CBUS values (see Table 5: SPI Hardware Settings on page 10). In x2 the CDIO pin is a bidirectional data I/O pin.

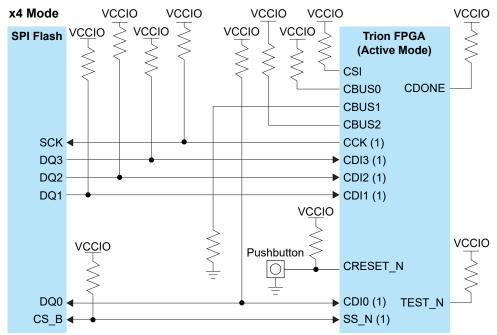

Figure 4: Active Quad (x4)

See Resistors in Configuration Circuitry on page 37 for the resistor values.

#### Note:

1. The external pull-up is optional unless required by an external load.

#### **Timing**

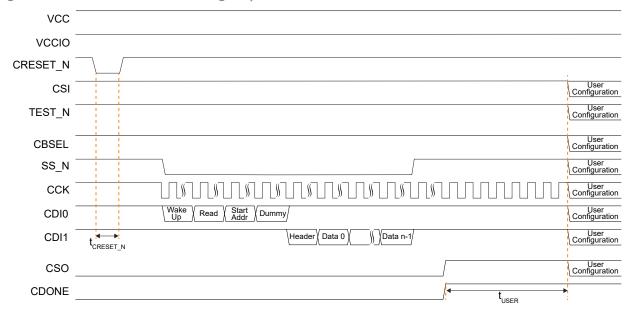

The FPGA supplies the configuration clock and issues instructions to interact with an external flash through the SPI pins. When the FPGA powers up and enters active mode, SS N is a weak pullup. Then, the FPGA:

- 1. Starts configuration by driving SS\_N low to wake up the external SPI flash.

- 2. Issues a release from power-down instruction to wake up the external SPI flash by driving the CDIO pin.

- 3. Waits for at least 30 µs.

- **4.** Issues a fast read command to read the content of SPI flash from address 24h'000000. The maximum SPI flash address width for configuration is 24 bits.

- **5.** Optional: when configuration completes, the FPGA issues a deep power-down instruction to force the external SPI flash to enter into deep power-down state.

Figure 5: SPI Active Mode (x1) Timing Sequence

**Note:** The waveforms are in control block perspective without any optional external pull-up or pull-down resistor connected.

**Learn more:** Refer to the Trion® FPGA data sheet for timing specifications.

### SPI Active Mode for SIP Packages

Trion® FPGAs in QFP100F3 packages are a system-in-package (SIP) that includes an internal SPI flash which you can use to store configuration bitstreams. However, you can still use an external SPI flash to store the configuration bitstreams.

Depending on the setup, you must observe the following pin connection requirements in addition to the connections shown in Connection Examples on page 13:

Table 9: Additional Connection Requirements for SIP Packages

| Configuration Setup                | SPI_CS_N Pin                | External Flash Chip Select Pin |

|------------------------------------|-----------------------------|--------------------------------|

| Configure with internal flash only | Connect to Trion® SS_N pin  | Not applicable                 |

| Configure with internal flash      | Connect to Trion® SS_N pin  | Connect any Trion® GPIO pin    |

| Configure with external flash      | Connect any Trion® GPIO pin | Connect to Trion® SS_N pin     |

#### SPI Active Mode without CSI

Trion® FPGAs in smaller pin count packages, such as the WLCSP80 and BGA169, may not have the CSI signals bonded out. This pinout limits your programming options. Without CSI, you cannot enable or disable the FPGA from another host such as a microprocessor. Additionally, you cannot cascade configuration.

The schematics for programming without CSI are the same as the regular SPI active schematics except that you do not connect the CSI signal.

### Clocking

An internal oscillator generates the internal clocks the FPGA uses during configuration. In SPI active configuration mode, configuration starts operating at the default frequency (10 MHz) and then switches to the user-selected clock to minimize configuration time (assuming the SPI flash device supports the faster  $f_{\rm MAX}$ ).

You set the configuration clock frequency in the Efinity<sup>®</sup> software.

**Table 10: Internal Oscillator Clock Settings**

| SPI Clock Divider | Frequency (MHz) |

|-------------------|-----------------|

| DIV4              | 20              |

| DIV8              | 10              |

### **SPI** Passive Mode

In passive mode, the FPGA receives the configuration clock and data from an external active module such as an external microprocessor or microcontroller. This mode supports a data width of up to 32 bits.

**Learn more:** Refer to the Trion<sup>®</sup> device data sheet for the widths your device supports.

Design considerations are similar to active configuration except CCK must be driven from an external clock source. Each configuration image contains a synchronization pattern. When the Trion® FPGA detect the synchronization pattern, it begins configuration. The external active device must supply data continuously on every clock until configuration ends.

Note: Efinix recommends that you use the same VCCIO on the banks of all configuration pins.

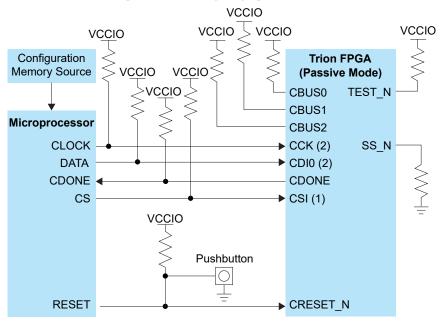

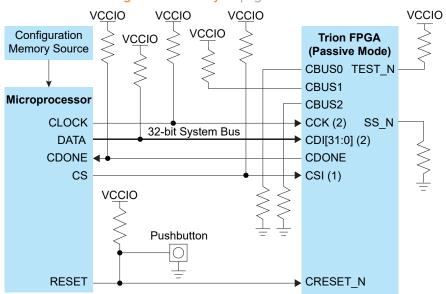

#### **Connection Examples**

These examples show SPI passive x1 and x32 modes. For other modes, set the value of CBUS [2:0] according to Table 5: SPI Hardware Settings on page 10.

**Learn more:** Refer to Trion Hardware Design Checklist and Guidelines for the detailed connection requirements.

Figure 6: Passive (x1)

See Resistors in Configuration Circuitry on page 37 for the resistor values.

#### Note:

- 1. You can connect the CSI pin to VCCIO as well as driving it from the microprocessor.

- 2. The external pull-up is optional unless required by an external load.

**Table 11: Bitstream Bits in Series**

| Bus Bit  | 0      |

|----------|--------|

| Cycle 1  | Bit 7  |

| Cycle 2  | Bit 6  |

| Cycle 3  | Bit 5  |

| Cycle 4  | Bit 4  |

| Cycle 5  | Bit 3  |

| Cycle 6  | Bit 2  |

| Cycle 7  | Bit 1  |

| Cycle 8  | Bit 0  |

| Cycle 9  | Bit 15 |

| Cycle 10 | Bit 14 |

| Cycle 11 | Bit 13 |

| Cycle 12 | Bit 12 |

| Cycle 13 | Bit 11 |

| Cycle 14 | Bit 10 |

| Cycle 15 | Bit 9  |

| Cycle 16 | Bit 8  |

Figure 7: Passive (x32)

See Resistors in Configuration Circuitry on page 37 for the resistor values.

#### Note:

- 1. You can connect the CSI pin to VCCIO as well as driving it from the microprocessor.

- 2. The external pull-up is optional unless required by an external load.

Table 12: Bitstream Bytes Packed into 32 bit Parallel Bus

| Bus Bit | 31 2   | 24 23 | 16     | 15 |        | 8 | 7 |        | 0 |

|---------|--------|-------|--------|----|--------|---|---|--------|---|

| Cycle 1 | Byte 0 |       | Byte 1 |    | Byte 2 |   |   | Byte 3 |   |

| Cycle 2 | Byte 4 |       | Byte 5 |    | Byte 6 |   |   | Byte 7 |   |

Table 13: Bitstream Bytes Packed into 16 bit Parallel Bus

| Bus Bit | 15     | 8 | 7      | 0 |

|---------|--------|---|--------|---|

| Cycle 1 | Byte 0 |   | Byte 1 |   |

| Cycle 2 | Byte 2 |   | Byte 3 |   |

| Cycle 3 | Byte 4 |   | Byte 5 |   |

| Cycle 4 | Byte 6 |   | Byte 7 |   |

Table 14: Bitstream Bytes Packed into 8 bit Parallel Bus

| Bus Bit | 7      |        | 0 |

|---------|--------|--------|---|

| Cycle 1 |        | Byte 0 |   |

| Cycle 2 | Byte 1 |        |   |

| Cycle 3 |        | Byte 2 |   |

| Cycle 4 |        | Byte 3 |   |

Table 15: Bitstream Bits Packed into 4 bit Parallel Bus

| Bus Bit | 3      | 2      | 1      | 0      |

|---------|--------|--------|--------|--------|

| Cycle 1 | Bit 7  | Bit 6  | Bit 5  | Bit 4  |

| Cycle 2 | Bit 3  | Bit 2  | Bit 1  | Bit 0  |

| Cycle 3 | Bit 15 | Bit 14 | Bit 13 | Bit 12 |

| Cycle 4 | Bit 11 | Bit 10 | Bit 9  | Bit 8  |

Table 16: Bitstream Bits Packed into 2 bit Parallel Bus

| Bus Bit | 1      | 0      |

|---------|--------|--------|

| Cycle 1 | Bit 7  | Bit 6  |

| Cycle 2 | Bit 5  | Bit 4  |

| Cycle 3 | Bit 3  | Bit 2  |

| Cycle 4 | Bit 1  | Bit 0  |

| Cycle 5 | Bit 15 | Bit 14 |

| Cycle 6 | Bit 13 | Bit 12 |

| Cycle 7 | Bit 11 | Bit 10 |

| Cycle 8 | Bit 9  | Bit 8  |

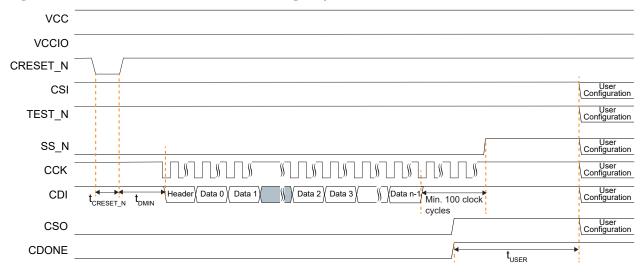

#### **Timing**

The microprocessor or microcontroller supplies the configuration clock and controls the reset signal. The microprocessor or microcontroller must hold CRESET\_N low for a duration of  $t_{\text{CRESET}\_N}$  and then release it to start the SPI passive configuration. After  $t_{\text{DMIN}}$ , the Trion® FPGA samples the synchronization pattern and begins configuration.

Figure 8: SPI Passive Mode (x1, Mode 3) Timing Sequence

### Note:

- The waveforms are in control block perspective without any optional external pull-up or pull-down resistor connected.

- CDI input data is clocked by CCK. CCK must stop toggling if the bit stream data becomes invalid

to prevent configuration failure. You must resume with the next bit stream data before stopping to

continue the configuration.

- CSI must stay high throughout the configuration.

- SS\_N must stay low throughout the configuration.

- Efinix does not recommend you to connect multiple slaves in the same SPI bus.

**Important:** To ensure successful configuration, the microprocessor must continue to supply the configuration clock to the Trion® FPGA for at least 100 cycles after sending the last configuration data.

**Learn more:** Refer to the Trion® FPGA data sheet for timing specifications.

**Learn more:** Refer to the AN 035: SPI Passive Programming with Raspberry Pi for a SPI passive programming example design.

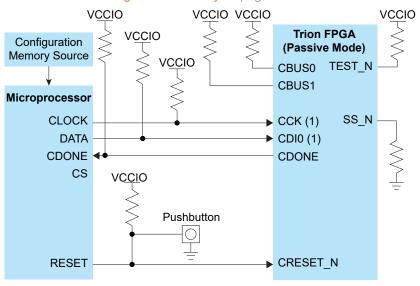

#### SPI Passive Mode without CSI or CBUS2

Trion® FPGAs in smaller pin count packages, such as the WLCSP80 and BGA169, may not have the CSI or CBUS2 signals bonded out. This pinout limits your programming options.

- Without CSI, you cannot enable or disable the FPGA from another host such as a microprocessor. Additionally, you cannot cascade configuration.

- Without CBUS2 you can still use CBUS0 and CBUS1 to program using the passive serial x1, x2, and x4 modes.

The following figures show the schematics for programming without CSI or CBUS2.

Figure 9: Passive (x1) without CSI or CBUS2

See Resistors in Configuration Circuitry on page 37 for the resistor values.

Note:

1. The external pull-up is optional unless required by an external load.

Figure 10: Passive (x2) without CSI or CBUS2

See Resistors in Configuration Circuitry on page 37 for the resistor values.

Note:

1. The external pull-up is optional unless required by an external load.

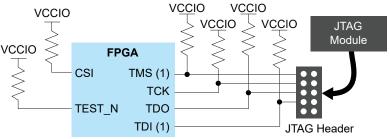

### JTAG Mode

The JTAG serial configuration mode is popular for prototyping and board testing. The fourpin JTAG boundary-scan interface is commonly available on board testers and debugging hardware.

This section describes the JTAG configuration mode, for JTAG boundary-scan testing, refer to AN 021: Performing Boundary-Scan Testing in Trion FPGAs.

**Learn more:** Refer to the following web sites for more information about the JTAG interface:

http://ieeexplore.ieee.org/document/6515989/ https://en.wikipedia.org/wiki/JTAG

**Table 17: Supported JTAG Instructions**

| Instruction    | Binary<br>Code [3:0] | Description                                        |  |

|----------------|----------------------|----------------------------------------------------|--|

| SAMPLE/PRELOAD | 0010                 | Enables the boundary-scan SAMPLE/PRELOAD operation |  |

| EXTEST         | 0000                 | Enables the boundary-scan EXTEST operation         |  |

| BYPASS         | 1111                 | Enables BYPASS                                     |  |

| IDCODE         | 0011                 | Enables shifting out the IDCODE                    |  |

| PROGRAM        | 0100                 | JTAG configuration                                 |  |

| ENTERUSER      | 0111                 | Changes the FPGA into user mode.                   |  |

| JTAG_USER1     | 1000                 | Connects the JTAG User TAP 1.                      |  |

| JTAG_USER2     | 1001                 | Connects the JTAG User TAP 2.                      |  |

| JTAG_USER3     | 1010                 | Connects the JTAG User TAP 3.                      |  |

| JTAG_USER4     | 1011                 | Connects the JTAG User TAP 4.                      |  |

**Learn more:** Refer to the AN 038: Programming with an MCU and the JTAG Interface for more information about programming Efinix<sup>®</sup> FPGAs with a microcontroller using JTAG mode.

Connect the FPGA pins as shown in the following diagrams.

Figure 11: JTAG Programming

See Resistors in Configuration Circuitry on page 37 for the resistor values.

Note:

1. The external pull-up is optional unless required by an external load.

The CRESET\_N signal needs to be deasserted before JTAG configuration begins. When configuration ends, the JTAG host issues the ENTERUSER instruction to the FPGA. After CDONE goes high and the FPGA receives the ENTERUSER instruction, the FPGA waits for  $t_{USER}$  to elapse, and then it goes into user mode.

**Note:** The FPGA may go into user mode before  $t_{USER}$  has elapsed. Therefore, you should keep the system interface with the FPGA in reset until  $t_{USER}$  has elapsed.

| Figure 1 | 2: JTAG Programming Waveform                                 |

|----------|--------------------------------------------------------------|

| VCC      |                                                              |

| VCCIO    |                                                              |

| CSI      |                                                              |

| TEST_N   |                                                              |

| TCK      |                                                              |

| TMS      | Capture   Shift   Capture   IR                               |

| TDI      | PROGRAM  D0 D1 D2 D3 D4 D5   Dn-2 Dn-1 Min. 100 clock cycles |

**Note:** The waveforms are in control block perspective and it is require to connect to weak internal pull-up resistors.

#### **Design Considerations**

- Because the TCK and TMS signals connect devices in the JTAG chain, they must have good signal quality.

- TCK should transition monotonically at the receiving devices and should be terminated correctly. Poor TCK quality can limit the maximum frequency you can use for configuration.

- Buffer TMS and TCK so they have sufficient drive strength at all receiving devices.

- Ensure that the logic high voltage is compatible with all devices in the JTAG chain.

- If your chain contains devices from different vendors, you might need to drive optional JTAG signals, such as TRST and enables.

- For Trion T4, T8, T13, T20 (WLCSP80, QFP100F3, QFP144, BGA256, and BGA169 packages) FPGAs:

- Assertion and deassertion of CRESET N is required prior to JTAG configuration.

- When using the Efinity programmer to perform JTAG configuration, the CRESET\_N and SS\_N pins are used in addition to the standard JTAG pins. However, they are not required when performing SPI flash programming through the JTAG bridge, or when performing other non-configuration JTAG functions.

**Learn more:** Refer to JTAG Programming Connections on page 41 for JTAG configuration connection examples and JTAG Programming on page 49 for details about JTAG programming using the Efinity Programmer.

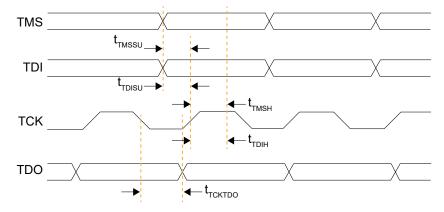

#### **Timing Parameters**

Figure 13: Boundary-Scan Timing Waveform

**Learn more:** Refer to the FPGA data sheet for timing specifications.

Refer to the Virtual I/O Debug Core section in the Efinity Software User Guide for more information about JTAG User TAP interface.

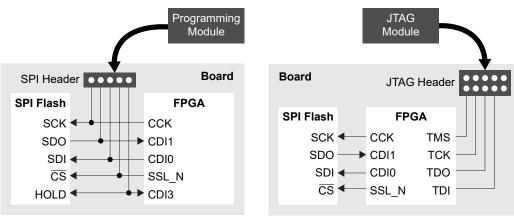

# Flash Programming Modes

The following table shows the methods you can use to program the configuration bitstream into the flash device on your board. Although you can program the flash directly using the SPI interface, this method requires that you have a SPI header on your board or use an FDTI chip. Therefore, Efinix recommends that you use a JTAG bridge, because that method only requires a JTAG header, which you would typically have on your board for other purposes anyway.

The Efinity software includes the JTAG SPI Flash Loader IP core that gives you full control over a SPI flash device and lets you perform actions comparable to an FTDI flash controller chip. With this IP core you can turn the FPGA into a flash programmer and use it to program the flash device.

Learn more: Refer to the JTAG SPI Flash Loader Core User Guide for more information.

**Table 18: Flash Programming Modes**

| Mode                                  | Description                                                                                                                                                                                                   |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPI Active (serial/parallel)          | Use the Efinity Programmer and a cable connected to a SPI header on the board.                                                                                                                                |

| SPI Active using JTAG Bridge (Legacy) | Program a single flash device. First, program the FPGA with a design that turns it into a flash programmer. Then, program the flash. This is the same mode that was in previous versions of Efinity software. |

| SPI Active using JTAG Bridge (New)    | A improved version of the SPI Active using JTAG Bridge (Legacy) mode with a faster flash programming time.                                                                                                    |

Figure 14: Flash Programming Board Setup

Using a SPI Header

Using a JTAG Header

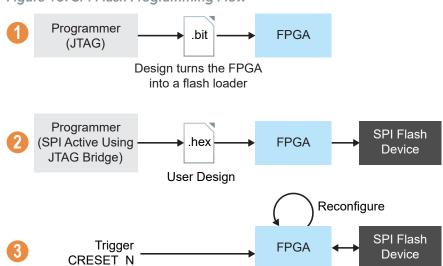

# Programming the Flash Using a JTAG Bridge

You can use the JTAG SPI Flash Loader to load a new user image into the SPI flash device on your board. The Trion® FPGA bridges the JTAG commands sent from the computer to the flash device. This mode lets you save board space because you can use the JTAG header on your board to program the flash instead of using a separate SPI header.

The flash programming flow consists of these steps:

- 1. Turn the Trion® FPGA into a flash programmer by configuring the FPGA via JTAG with the JTAG SPI Flash Loader IP core. You can configure the IP core using the Efinity IP Manager. You use a .bit bitstream file to configure the FPGA.

- 2. Use the Efinity Programmer and the SPI Active using JTAG Bridge mode to program the user image into the flash device. The Programmer sends the command through the Trion® FPGA, which in turn programs the flash. You use a .hex bitstream file for the user image.

- **3.** After the flash is programmed, toggle the Trion® FPGA's CRESET\_N signal to trigger reconfiguration using the new flash image.

Figure 15: SPI Flash Programming Flow

When using this mode, you need to connect the JTAG pins. Refer to the diagrams in Connecting a JTAG Mini Module and JTAG Programming Connections on page 41 for the pins to connect.

**Learn more:** For more information on using the JTAG SPI Flash Loader and the **SPI Active using JTAG Bridge** programming mode, refer to the **JTAG SPI Flash Loader Core User Guide**.

# Power Up

# Power Up Sequence

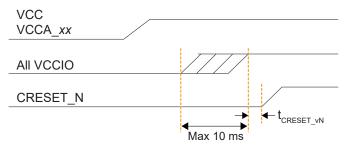

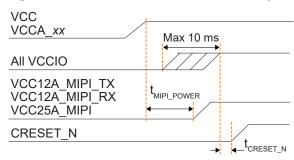

Efinix® recommends the following power up sequence when powering Trion® FPGAs:

Figure 16: Trion® FPGAs without MIPI Power Up Sequence

Figure 17: Trion® FPGAs with MIPI Power Up Sequence

- 1. Power up VCC and VCCA xx first.

- 2. When VCC and VCCA\_xx are stable, power up all VCCIO pins. There is no specific timing delay between the VCCIO pins.

- 3. For FPGAs with MIPI: Apply power to VCC12A\_MIPI\_TX, VCC12A\_MIPI\_RX, and VCC25A\_MIPI at least  $t_{MIPI\ POWER}$  after VCC is stable.

**Important:** Ensure the power ramp rate is within VCCIO/10 V/ms to 10 V/ms.

**4.** After all power supplies are stable, hold CRESET\_N low for a duration of t<sub>CRESET\_N</sub> before asserting CRESET\_N from low to high to trigger active SPI programming (the FPGA loads the configuration data from an external flash device).

When you are not using the GPIO, MIPI, DDR or PLL resources, connect the pins as shown in the following table.

Table 19: Connection Requirements for Unused Resources

| Unused Resource | Pin            | Note                                      |

|-----------------|----------------|-------------------------------------------|

| GPIO Bank       | VCCIOxx        | Connect to either 1.8 V, 2.5 V, or 3.3 V. |

| PLL             | VCCA_PLL       | Connect to VCC (1.2 V).                   |

| MIPI            | VCC12A_MIPI_TX | Connect to VCC (1.2 V).                   |

|                 | VCC12A_MIPI_RX | Connect to VCC (1.2 V).                   |

| Unused Resource | Pin         | Note                         |

|-----------------|-------------|------------------------------|

|                 | VCC25A_MIPI | Connect to VCC (1.2 V).      |

| DDR             | VCCIO_DDR   | Floating. Leave unconnected. |

|                 | DDR_VREF    | Connect to ground.           |

**Learn more:** Refer to Trion Hardware Design Checklist and Guidelines for connection requirements for unused resources.

**Note:** Refer to Configuration Timing and MIPI Power Up Timing sections in the Trion® FPGA data sheets for timing information.

# **Power Supply Current Transient**

You may observe an inrush current on the dedicated power rail during power-up. You must ensure that the power supplies selected in your board meets the current requirement during power-up and the estimated current during user mode. Use the Power Estimator to calculate the estimated current during user mode.

Table 20: Maximum Power Supply Current Transient for VCC

| FPGA | Package                                      | Maximum Power Supply<br>Current Transient <sup>(4)(5)</sup> (mA) |

|------|----------------------------------------------|------------------------------------------------------------------|

| T4   | All                                          | 18                                                               |

| Т8   | BGA49, BGA81                                 | 18                                                               |

|      | QFP144                                       | 35                                                               |

| T13  | All                                          | 35                                                               |

| T20  | WLCSP80, QFP100F3,<br>QFP144, BGA169, BGA256 | 35                                                               |

|      | BGA324, BGA400                               | 57                                                               |

| T35  | All                                          | 57                                                               |

| T55  | All                                          | 200                                                              |

| T85  | All                                          | 200                                                              |

| T120 | All                                          | 200                                                              |

<sup>(4)</sup> Inrush current for other power rails are not significant in Trion® FPGAs.

<sup>(5)</sup> Measured at room temperature.

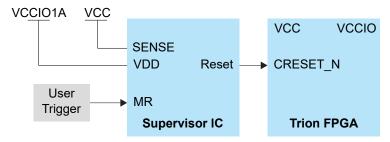

# Power Up Circuitry Recommendation

You can use one of the following methods to hold the CRESET\_N pin of the Trion® FPGA low after the power supplies are stable:

- Supervisor integrated circuit (IC)

- Microprocessor or microcontroller

**Important:** Do not drive a signal to any Trion® I/O pins before the Trion® FPGA is powered up. Most FPGAs have electrostatic discharge (ESD) circuits to protect the devices from ESD events. Driving the I/O pins before VCCIO will result in an in-rush current driving the I/Os to a specific voltage through the ESD circuit to the VCCIO rail. Trion® FPGAs will remain in configuration mode after power-up if this unexpected voltage exists on the CRESET\_N due to the improper power-up sequence.

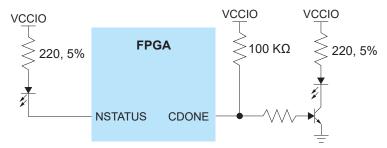

#### Supervisor IC Circuitry Example

Assuming that the VCCIO1A is the last power supply to be stable in the system, the supervisor IC must hold the CRESET\_N pin low for a duration of  $t_{RP}$  (reset timeout period) after the VCCIO1A reaches the stable threshold.

Ensure that the  $t_{RP}$  of the selected supervisor IC is more than the required  $t_{CRESET\_N}$ . Refer to the supervisor IC vendor for the recommended operating circuitry.

Figure 18: Supervisor IC Power Up Circuitry

**Note:** The user trigger (pushbutton, FTDI module) must be connected to the MR pin of the supervisor IC.

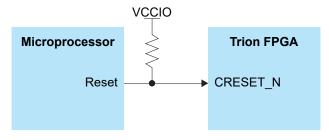

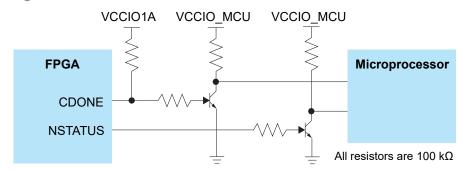

#### Microprocessor or Microcontroller Circuitry Example

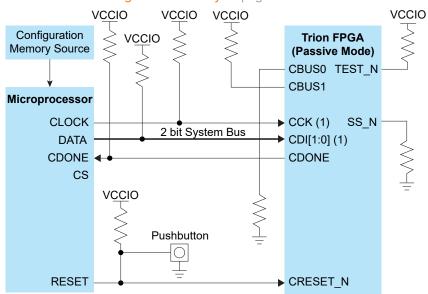

Figure 19: Microprocessor Power Up Circuitry

See **Resistors in Configuration Circuitry** on page 37 for the resistor values.

The microprocessor or microcontroller must hold the  $CRESET_N$  pin low more than the required  $t_{CRESET_N}$  duration.

# Configuration Sequence

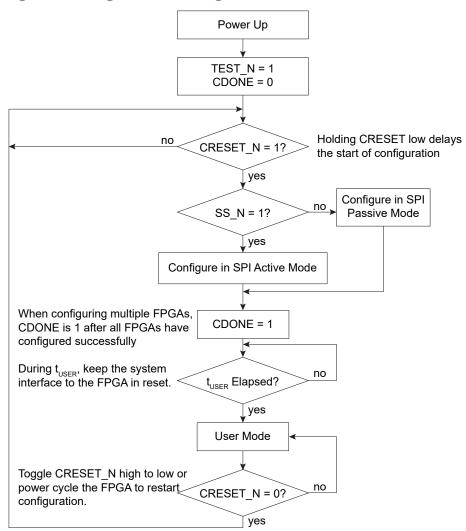

The Trion® FPGA configuration logic uses the following sequence during configuration:

1. When CRESET\_N returns high (logic 1) after being held low (logic 0), the FPGA samples the logical value on its SS\_N pin. Like other programmable I/O pins, the SS\_N pin has an internal pull-up resistor.

**Learn more:** Refer to the Trion $^{\textcircled{@}}$  data sheet for the pulse width requirements of CRESET N.

- 2. If the SS\_N pin is sampled as a logic 1 (high), the FPGA configures using the SPI active configuration interface.

- 3. If the SS\_N pin is sampled as a logic 0 (low), the FPGA waits to be configured from an external controller or from another FPGA in SPI active configuration mode using an SPI-like interface.

Figure 20: Configuration Flow Diagram

# Support for Multiple Images

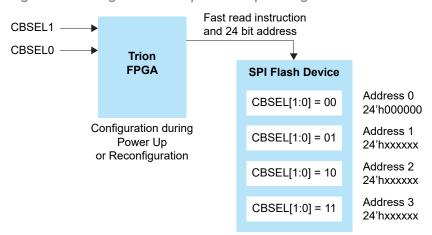

When powered up in SPI active mode, the default action is for an image stored at address 0 to configure the Trion® FPGA. If you enable the multi-image feature, you can optionally choose from three other images.

**Learn more:** To enable the multi-image feature, use the Efinity Programmer to combine multiple images into a single hex file. See **Program Multiple Images (CBSEL)** on page 46 for more information.

During multi-image configuration, the Trion® FPGA monitors the CBSEL[1:0] pin logic value when configuration or reconfiguration begins to determine which bitstream image to use. Then, it loads the corresponding image starting from the address specified in the bitstream option bits by sending out a fast read instruction followed by the address.

For multi-image configuration, the Efinity® software saves the images to the bitstream file with no configuration bits between images.

**Note:** Some Trion® FPGAs may not support multiple images for all configuration modes. The Supported Configuration Modes topic in your data sheet explains which modes the FPGA supports.

Figure 21: Configuration Setup for Multiple Images

Connect CBSEL[1:0] for the image you want to use:

- 00 for image 1

- 01 for image 2

- 10 for image 3

- 11 for image 4

During configuration, the FPGA initially searches for a valid image starting at the memory location  $0 \times 0000\_0000$  in the SPI flash. It then proceeds to read the memory location based on the CBSEL[1:0] setting. If no valid image is found at that memory location, the FPGA continues to search in ascending order until it locates a valid image. For example, if CBSEL[1:0] is set to 11 and the SPI flash only contains valid images for 00 and 01, the FPGA will load the image from 00. The address for image 00 must be  $0 \times 0000\_0000$ . The following table describes valid and invalid images.

| Image Details                                                                     | Note                                                                                                                                                                           |  |

|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Correct synchronization pattern and CRC                                           | Image is valid and configuration performs as expected.                                                                                                                         |  |

| Corrupted synchronization pattern                                                 | Image is invalid. The FPGA continues to search in ascending order until it locates an image with a valid synchronization pattern. The FPGA is then configured with that image. |  |

| Correct synchronization pattern<br>but corrupted data resulting in a<br>CRC error | Image is invalid. The FPGA configuration will fail.                                                                                                                            |  |

**Learn more:** You can also use the internal reconfiguration feature to reconfigure the FPGA with a different image. This feature uses internal logic instead of the CBSEL[1:0] pins. Refer to AN 010: Using the Internal Reconfiguration Feature to Remotely Update Trion® and Titanium FPGAs for details on this feature.

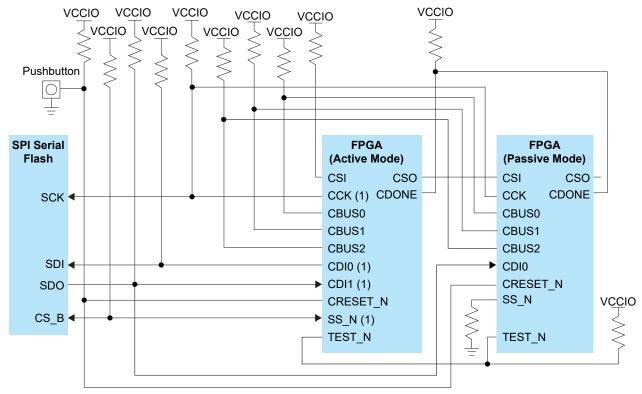

# Configuring Multiple FPGAs

If your application uses multiple Trion® FPGAs, you can configure all of them using a single configuration source.

- FPGAs that use the same configuration file can be loaded at the same time.

- FPGAs that use *different* configuration files (images) can be loaded sequentially, either through Trion® FPGAs in a daisy chain, or using external logic.

For daisy chain configurations, the Efinity® software includes 2,048 configuration bits between images in the bitstream file.

**Note:** You cannot daisy chain packages that do not have the CSI signal bonded out (such as the WLCSP80 and BGA169).

# Daisy Chaining with a SPI Flash Device

In a daisy chain, the FPGA closest to the configuration data source is the most upstream FPGA and the FPGA furthest from the source is the most downstream FPGA. The most upstream FPGA typically provides the configuration clock. All other FPGAs are in passive serial mode.

**Important:** Do not connect the NSTATUS pins of multiple FPGAs together when configuring in daisy chain configuration.

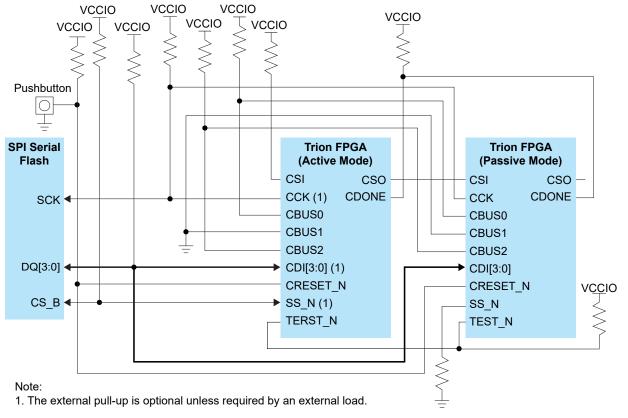

Figure 22: Serial Daisy Chain Configuration Interface Example

See **Resistors in Configuration Circuitry** on page 37 for the resistor values.

Note:

1. The external pull-up is optional unless required by an external load.

Figure 23: Parallel Daisy Chain Configuration (x4) Interface Example

See Resistors in Configuration Circuitry on page 37 for the resistor values.

(!)

**Important:** For parallel daisy chain x2 and x4, you are required to set the active configuration clock frequency,  $f_{MAX\ M}$ , to DIV4 (20 MHz).

# Daisy Chaining with a Microcontroller or Microprocessor

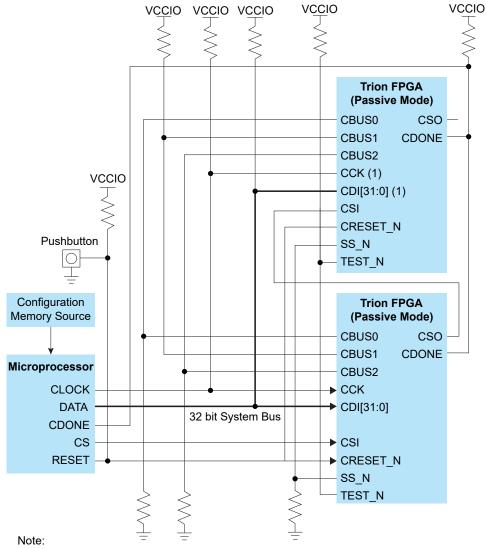

A microcontroller or microprocesser can configure FPGAs in a daisy chain with a single cascaded bitstream file. All FPGAs must be in passive mode.

This example shows serial daisy chain configuration with SPI passive x32 mode. For other modes, set the value of CBUS [2:0] according to Table 5: SPI Hardware Settings on page 10

(!)

**Important:** Do not connect the NSTATUS pins of multiple FPGAs together when configuring in daisy chain configuration.

Figure 24: Serial Daisy Chain Configuration (x32 Passive Mode) Interface Example

See Resistors in Configuration Circuitry on page 37 for the resistor values.

1. The external pull-up is optional unless required by an external load.

## Resistors in Configuration Circuitry

Efinix recommends that you use 10 k $\Omega$  for all unspecified pull-up and pull-down resistors in configuration circuitries.

Alternatively, you can calculate your own pull-up or pull-down resistance, R<sub>USER</sub>, shown in the following sections.

**Learn more:** The internal weak pull-up resistance, internal weak pull-down resistance, and Schmitt Trigger thresholds values used in the following formulas are included in the Trion Data Sheet in **Support Center**.

### User-Defined Pull-Up Resistor Values

$$R_{USER} = (R_{CPU} * R_{IPU}) / (R_{IPU} - R_{CPU})$$

#### where:

- R<sub>USER</sub> = User-defined pull-up resistance

- R<sub>CPU</sub> = Combined pull-up resistance

- R<sub>IPU</sub> = Internal weak pull-up resistance

The combined pull-up resistance, R<sub>CPU</sub>, can be derived using the following formula:

$$VT+ \leq VCCIO *(R_{IPD} / (R_{CPU} + R_{IPD}))$$

#### where:

- VT+ = Schmitt Trigger low-to-high threshold

- VCCIO = I/O bank power supply

- R<sub>IPD</sub> = Internal weak pull-down resistance

#### User-Defined Pull-Down Resistor Values

$$R_{USER} = (R_{CPD} * R_{IPD}) / (R_{IPD} - R_{CPD})$$

#### where:

- R<sub>USER</sub> = User-defined pull-down resistance

- R<sub>CPD</sub> = Combined pull-down resistance

- R<sub>IPD</sub> = Internal weak pull-down resistance

The combined pull-down resistance, R<sub>CPD</sub>, can be derived using the following formula:

$$VT \ge VCCIO *(R_{CPD} / (R_{CPD} + R_{IPU}))$$

#### where:

- VT- = Schmitt Trigger high-to-low threshold

- VCCIO = I/O bank power supply

- R<sub>IPU</sub> = Internal weak pull-up resistance

# **Configuration Timing**

Trion® FPGA configuration timing is process dependent. The following tables show the timing parameters for the various configuration modes.

**Important:** Refer to the data sheet for your Trion® FPGA for the timing specifications for these parameters.

#### Table 21: All Modes

| Symbol                | Parameter                                                                       |  |

|-----------------------|---------------------------------------------------------------------------------|--|

| t <sub>CRESET_N</sub> | Minimum CRESET_N low pulse width required to trigger re-configuration.          |  |

| t <sub>USER</sub>     | Minimum configuration duration after CDONE goes high before entering user mode. |  |

#### Table 22: Active Mode

| Symbol             | Parameter                                  |  |

|--------------------|--------------------------------------------|--|

| f <sub>MAX_M</sub> | Active mode configuration clock frequency. |  |

| t <sub>SU</sub>    | Setup time.                                |  |

| t <sub>H</sub>     | Hold time.                                 |  |

#### Table 23: Passive Mode

| Symbol Parameter   |                                                                                 |  |

|--------------------|---------------------------------------------------------------------------------|--|

| f <sub>MAX_S</sub> | Passive mode configuration clock frequency.                                     |  |

| t <sub>CLKH</sub>  | Configuration clock pulse width high.                                           |  |

| t <sub>CLKL</sub>  | Configuration clock pulse width low.                                            |  |

| t <sub>SU</sub>    | Setup time.                                                                     |  |

| t <sub>H</sub>     | Hold time.                                                                      |  |

| t <sub>DMIN</sub>  | Minimum time between deassertion of CRESET_N to first valid configuration data. |  |

#### Table 24: JTAG Mode

| Symbol              | Parameter                       |  |

|---------------------|---------------------------------|--|

| f <sub>TCK</sub>    | TCK frequency.                  |  |

| t <sub>TDISU</sub>  | TDI setup time.                 |  |

| t <sub>TDIH</sub>   | TDI hold time.                  |  |

| t <sub>TMSSU</sub>  | TMS setup time.                 |  |

| t <sub>TMSH</sub>   | TMS hold time.                  |  |

| t <sub>TCKTDO</sub> | TCK falling edge to TDO output. |  |

## Selecting the Right SPI Flash Device

Trion® FPGAs support an SPI flash memory interface for active mode configuration. Use these guidelines to help choose the correct flash device for your Trion® FPGA.

- Configuration Bits—Ensure that your chosen flash device has enough bits to store the

configuration bitstream.

- Single image—Find the configuration bits a single image uses (refer to Table 1: Trion FPGA Bitstream Size on page 4).

- Multiple images—Find the configuration bits a single image uses (refer to Table 1: Trion FPGA Bitstream Size on page 4). Multiply the number of bits times the number of images to determine the total bits required to store the full bitstream.

- Daisy chain—Use the formula  $(i \times b) + (2048 \times (i 1))$  where i is the number of images and b is the configuration bits for each image. For example, a daisy chain of three T8 FPGAs uses  $(3 \times 1,386,584) + (2,048 \times (3-1)) = 4,159,752 + 4,096 = 4,163,848$  bits.

- Configuration Bus Width—Determine the supported configuration bus width for the SPI flash device in Table 5: SPI Hardware Settings on page 10.

- SPI Clock Frequency—Ensure that your SPI flash device supports a clock frequency that is higher than the SPI active configuration clock frequency as described in Table 10: Internal Oscillator Clock Settings on page 16.

- Required Voltage—Make sure the voltage your SPI flash device requires is the same as the FPGA I/O bank voltage.

- **Temperature Range**—Check that the SPI flash device's temperature range is compatible with the operating temperature as described in the FPGA data sheet.

## Supported Flash Devices

Table 25: Supported Flash Devices

| Manufacturer                | Family Part Number                    |

|-----------------------------|---------------------------------------|

| GigaDevice                  | GD25Q, GD25WQ, and GD25LQ             |

| Macronix                    | MX25L, MX25U, MX25V, MX75L, and MX75U |

| Puya Semiconductor          | P25Q                                  |

| Winbond                     | W25Q                                  |

| Micron                      | M25P and MT25Q                        |

| XTX                         | XT25F                                 |

| Atmel (Adesto Technologies) | AT25SF                                |

| ISSI                        | IS25LP128                             |

**Note:** Efinix recommends using SPI NOR flash memories.

## Connecting Programming Hardware

You can program Efinix FPGA or the SPI flash using FTDI Mini Modules. This section describes the hardware connections required. See **Using the Efinity Programmer** on page 43 for instructions about SPI and JTAG programming using the Efinity® Programmer.

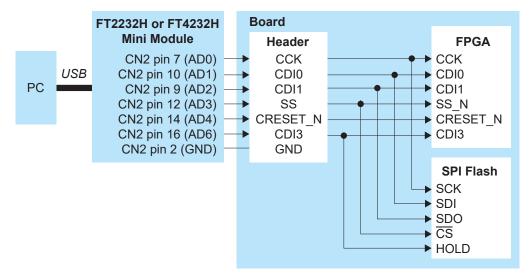

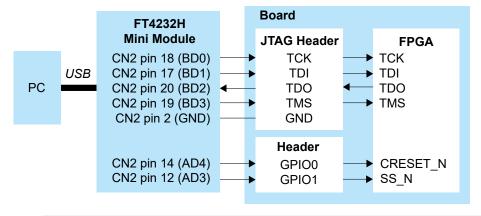

### **SPI Programming Connections**

The following figure illustrates the connection required when programming the SPI flash with FTDI FT2232H and FT4232H Mini Module.

Figure 25: SPI Flash Programming with FTDI FT2232H and FT4232H Mini Module Connections

### JTAG Programming Connections

### Connecting a JTAG Cable

Efinix does not recommend using the FTDI cable C232HM-DDHSL-0 for JTAG programming due to the possibility of the FPGA not being recognized or the potential for programming failures.

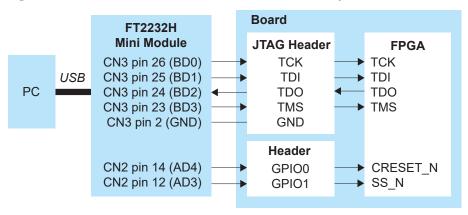

### Connecting a JTAG Mini Module

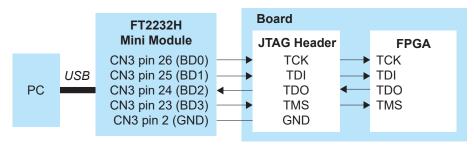

When programming T4, T8, T13, T20WLCSP80, T20QFP100F3, T20QFP144, T20BGA256, and T20BGA169 FPGAs, use this connection:

Figure 26: Connect FT2232 Mini Module to JTAG Pins plus CRESET\_N and SS\_N

Figure 27: Connect FT4232 Mini Module to JTAG Pins plus CRESET\_N and SS\_N

Note: This figure uses the CRESET\_N and SS\_N pins in addition to the standard JTAG pins. However, this setup is only needed for JTAG configuration. You can use the standard 4 JTAG pins and any cable for other JTAG functions.

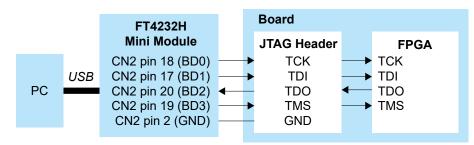

When programming T20BGA324, T20BGA400, T35, T55, T85, and T120 FPGAs, use this connection:

Figure 28: Connect FT2232 Mini Module to JTAG Pins

Figure 29: Connect FT4232 Mini-Module to JTAG Pins

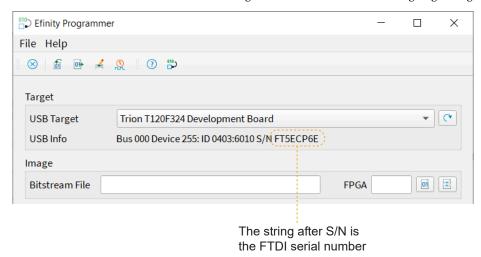

## Using the Efinity Programmer

The Efinity® software has a Programmer you use to configure Trion® FPGAs. You can run the Programmer using the GUI or with the command line.

## Generate a Bitstream (Programming) File

When you run the automated flow, the software automatically generates bitstream files that you can use to configure your target device. You can also generate the bitstream files manually. To generate bitstream files from the command line, use the following command:

#### **Example: Generate a Bitstream File from the Command Line**

Linux:

```

> efx run.py <project name>.xml --flow pgm

```

#### Windows:

```

> efx run.bat <project name>.xml --flow pgm

```

The software generates these files in the **outflow** directory:

- .hex file as < project name > .hex. Use this file to program in SPI active or passive mode.

- .bit file as < project name > .bit. Use this file for JTAG programming.

- [] Important: With the Efinity software v2021.2 and higher, you must use .hex for SPI and .bit for JTAG.

The bitstream file includes programming options you set for your project (e.g., to initialize user memory or set configuration mode). If you change these options you must regenerate the bitstream file. See Project-Based Programming Options on page 56.

**Note:** The software does not generate bitstream files for preliminary devices.

### Working with Bitstreams

You can use the Efinity Programmer to manipulate a bitstream before programming an FPGA or flash device.

### Edit the Bitstream Header

You can use the Programmer to edit the bitstream header information, for example, to add project or revision information. To edit the header:

- 1. In the Programmer, choose File > Edit Header... or click the toolbar icon to open the Edit Image Header dialog box. The window shows the default header information.

- 2. Edit the header.

- 3. Click Save.

**Important:** When editing the bitstream header, if you remove any of the auto-generated information (such as Device: <name>), the Programmer may not be able to recognize the bitstream. Efinix recommends that you only append a small amount of information to the auto-generated data if you want to customize or annotate the header. The header can be a maximum of 256 characters, including the auto-generated text.

If you want to write your own program to detect which device the bitstream targets (e.g., using a microprocessor and SPI passive mode), be sure to keep all of the auto-generated header, specifically the Device: <name> string.

### Export to Raw Binary Format

The Efinity® software v2018.4 and later supports raw binary (.bin) format for use with third-party flash programmers. To export to this format:

- 1. Open the Programmer.

- 2. Select the bitstream file.

- 3. Click Export.

- 4. Specify the filename.

- 5. Click Save.

You can also convert the file to .bin at the command line as described in Convert to Intel Hex Format at the Command Line on page 45.

### Export to .svf Format

The Efinity® software v2021.1 and later supports serial vector format (.svf) files for use with third-party JTAG programmers. To export to this format:

- 1. Open the Programmer.

- 2. Select a bitstream file.

- 3. Click Export.

- 4. Specify the filename.

- 5. Choose Serial Vector Format (\*.svf) as the Files of type.

- 6. Click Save.

**Note:** For more information on using this bitstream format, refer to Working with JTAG .svf Files section of the Efinity® Programmer user Guide.

You can also convert the file to **.hex** at the command line as described in **Convert to Intel Hex Format at** the **Command Line** on page 45.

### Convert to Intel Hex Format at the Command Line

You can also convert a bitstream file to Intel Hex and other formats at the command line using this command:

```

export_bitstream.py [-h] [--family <Trion or Titanium>] [--idcode IDCODE] [--freq FREQ]

[--sdr_size SDR_SIZE][--tir_length TIR_LENGTH] [--hir_length HIR_LENGTH]

[--tdr_length TDR_LENGTH] [--hdr_length HDR_LENGTH] [--enter_user_mode <on or off>]

<format> <input filename> <output filename>

```

#### Where *< format >* is:

- hex to bin

- hex to intelhex

- bin to hex

- intelhex to hex

- hex to svf

#### For example:

#### Combine Bitstreams and Other Files

You may want to store multiple bitstreams or other data into the same flash device on your board. For example, you can combine files for:

- Multi-image configuration using the CBSEL pins

- Internal reconfiguration

- Programming FPGAs in a daisy chain

- Programming a bitstream and other files such as a RISC-V application binary

You use the **Combine Multiple Image Files** dialog box to choose files to combine into a single file for programming. Choose one of the following modes:

Table 26: Modes when Combining Images